Quad-SPI interface (QUADSPI) RM0440

592/2126 RM0440 Rev 4

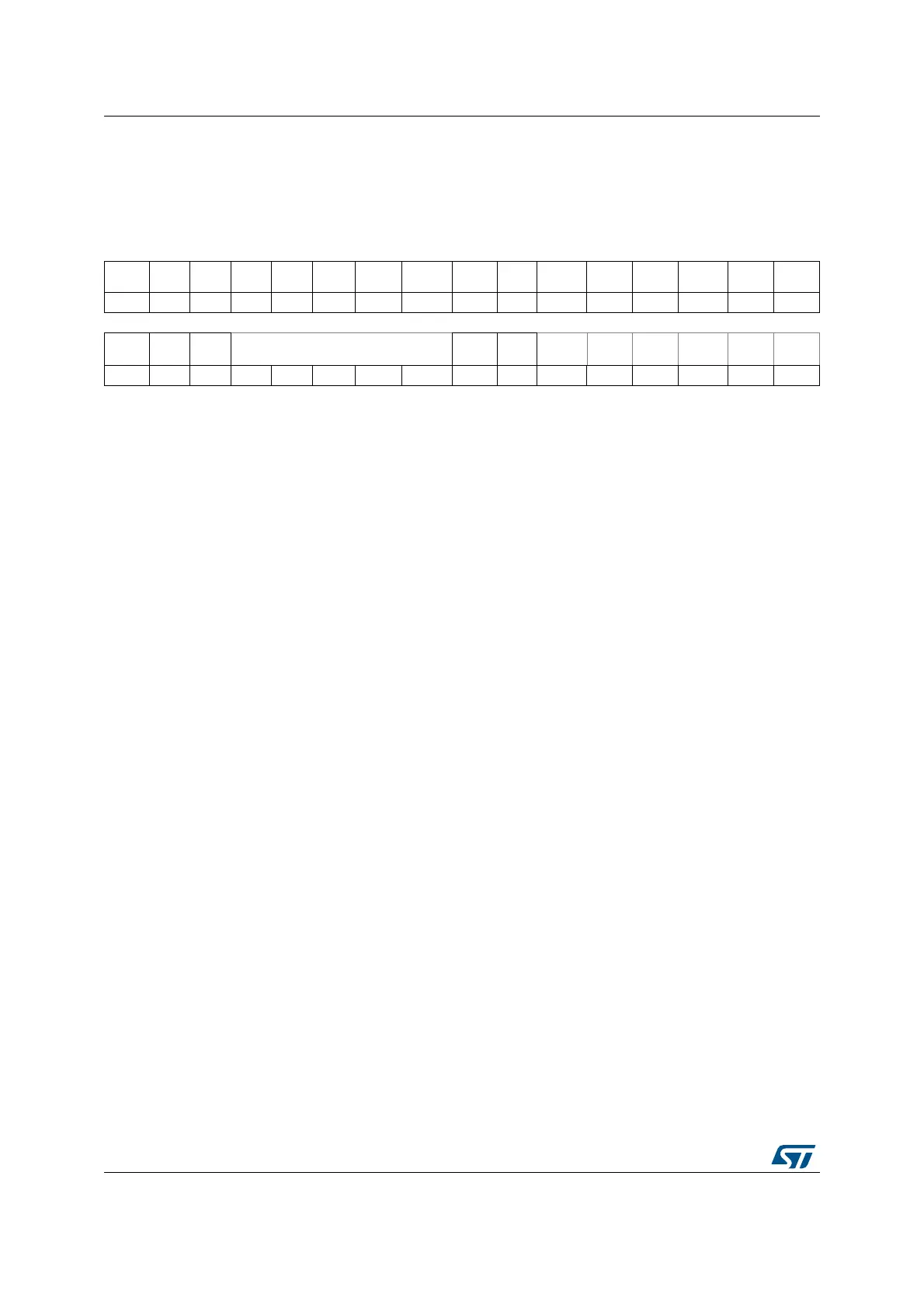

20.5.3 QUADSPI status register (QUADSPI_SR)

Address offset: 0x0008

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. FLEVEL[4:0] Res. Res. BUSY TOF SMF FTF TCF TEF

rr r r r r r r r r r

Bits 31:13 Reserved, must be kept at reset value.

Bits 12:8 FLEVEL[4:0]: FIFO level

This field gives the number of valid bytes which are being held in the FIFO. FLEVEL = 0

when the FIFO is empty, and 16 when it is full. In memory-mapped mode and in

automatic status polling mode, FLEVEL is zero.

Bits 7:6 Reserved, must be kept at reset value.

Bit 5 BUSY: Busy

This bit is set when an operation is on going. This bit clears automatically when the

operation with the Flash memory is finished and the FIFO is empty.

Bit 4 TOF: Timeout flag

This bit is set when timeout occurs. It is cleared by writing 1 to CTOF.

Bit 3 SMF: Status match flag

This bit is set in automatic polling mode when the unmasked received data matches the

corresponding bits in the match register (QUADSPI_PSMAR). It is cleared by writing 1

to CSMF.

Bit 2 FTF: FIFO threshold flag

In indirect mode, this bit is set when the FIFO threshold has been reached, or if there is

any data left in the FIFO after reads from the Flash memory are complete. It is cleared

automatically as soon as threshold condition is no longer true.

In automatic polling mode this bit is set every time the status register is read, and the bit

is cleared when the data register is read.

Bit 1 TCF: Transfer complete flag

This bit is set in indirect mode when the programmed number of data has been

transferred or in any mode when the transfer has been aborted.It is cleared by writing 1

to CTCF.

Bit 0 TEF: Transfer error flag

This bit is set in indirect mode when an invalid address is being accessed in indirect

mode. It is cleared by writing 1 to CTEF.

Loading...

Loading...