High-resolution timer (HRTIM) RM0440

986/2126 RM0440 Rev 4

27.5.20 HRTIM timer x compare 1 compound register (HRTIM_CMP1CxR)

(x = A to F)

Address offset: Block A: 0x0A0

Address offset: Block B: 0x120

Address offset: Block C: 0x1A0

Address offset: Block D: 0x220

Address offset: Block E: 0x2A0

Address offset: Block F: 0x320

Reset value: 0x0000 0000

27.5.21 HRTIM timer x compare 2 register (HRTIM_CMP2xR) (x = A to F)

Address offset: Block A: 0x0A4

Address offset: Block B: 0x124

Address offset: Block C: 0x1A4

Address offset: Block D: 0x224

Address offset: Block E: 0x2A4

Address offset: Block F: 0x324

Reset value: 0x0000 0000

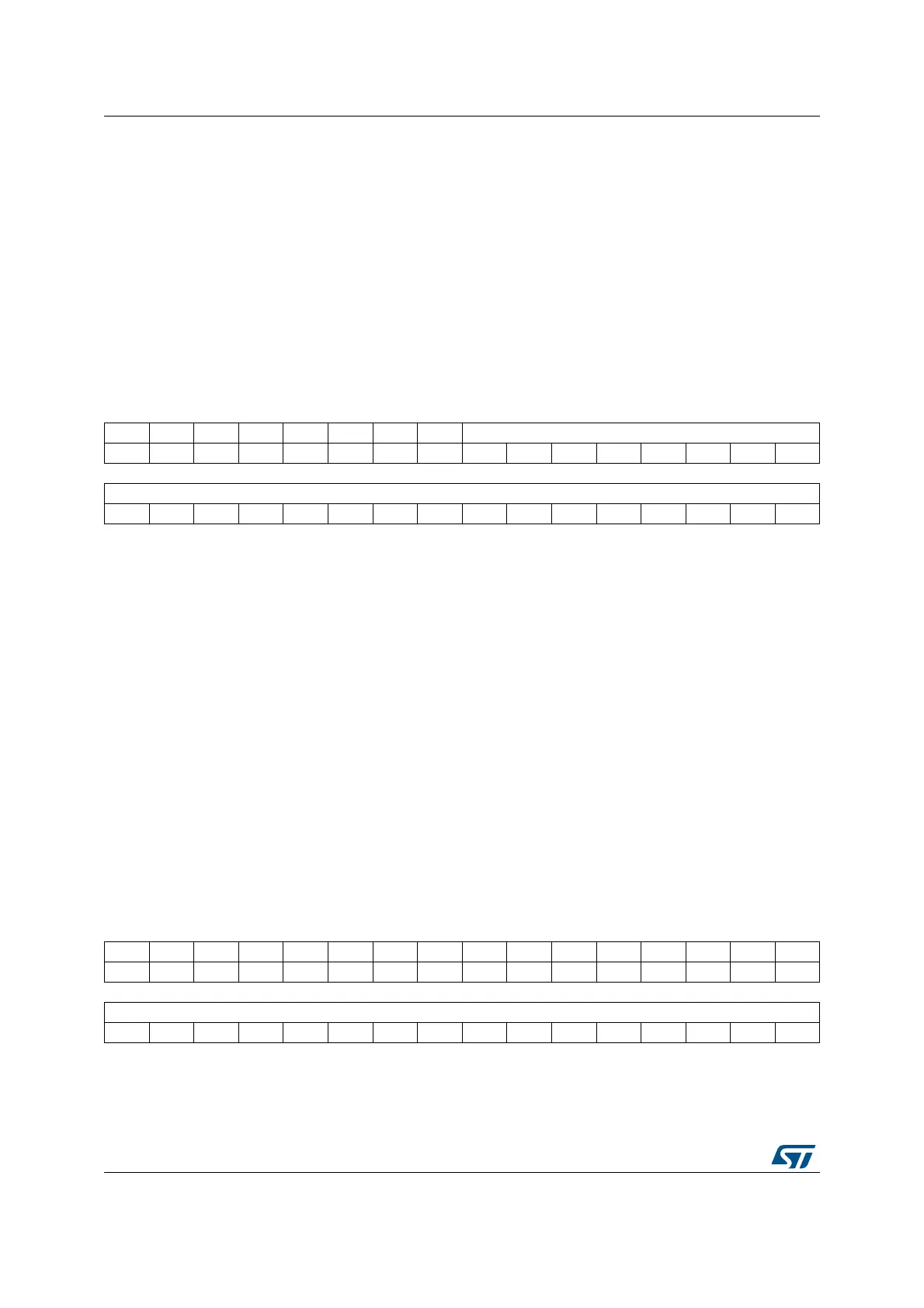

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. REPx[7:0]

rw rw rw rw rw rw rw rw

1514131211109876543210

CMP1x[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:24 Reserved, must be kept at reset value.

Bits 23:16 REPx[7:0]: Timer x repetition value (aliased from HRTIM_REPx register)

This bitfield is an alias from the REPx[7:0] bitfield in the HRTIMx_REPxR register.

Bits 15:0 CMP1x[15:0]: Timer x compare 1 value

This bitfield is an alias from the CMP1x[15:0] bitfield in the HRTIMx_CMP1xR register.

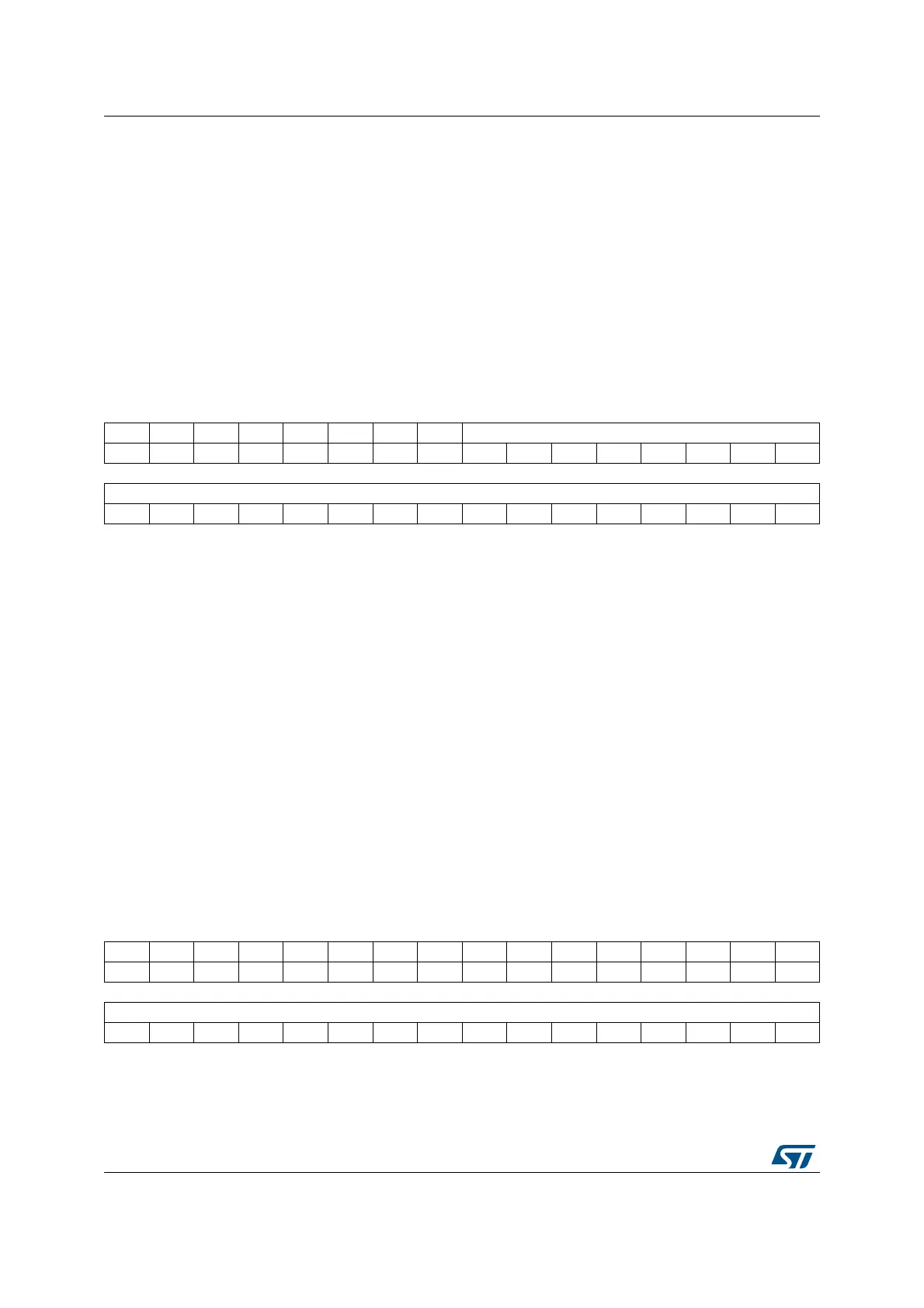

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

CMP2x[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...