304Tibbo Project System (TPS)

© Tibbo Technology Inc.

7.2.9.19

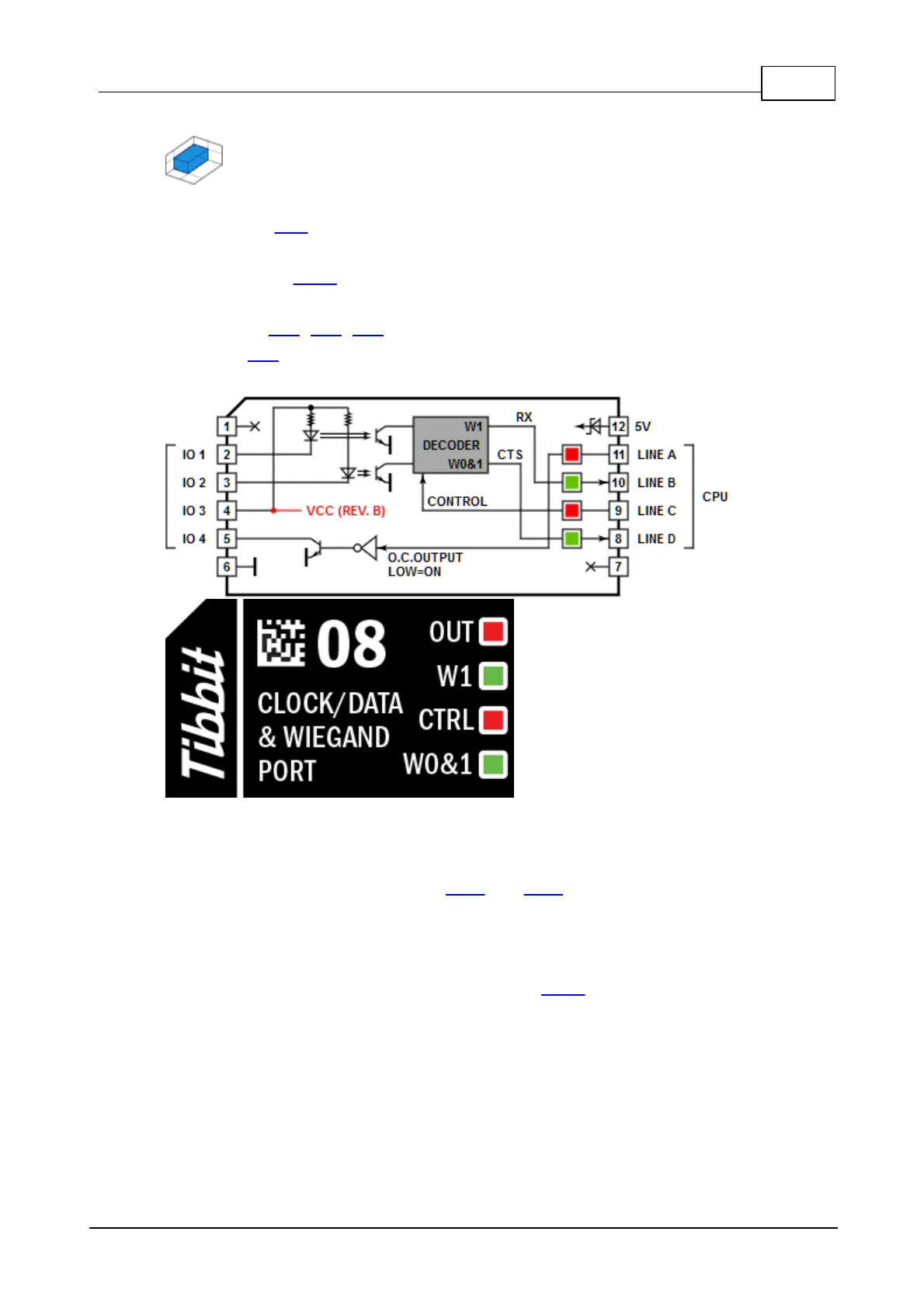

#08, M1S: Wiegand and Clock/Data Reader Port

Function: Wiegand and clock/data reader port plus one open collector output

Form factor: M1S

Category: Input/output module

Special needs: [SER]

Power requirements: 5V/20mA

Mates with: #19, #20, #21 (limited use)

See also: #11

Details

Our programmable devices (such as TPP2 and TPP3) have the unique ability to

process input from card readers with clock/data or Wiegand interface. This is

achieved through the ser. object running in the clock/data or Wiegand mode. Tibbit

#08 implements necessary hardware.

In order to be able to process card reader output, this Tibbit has to be connected

to the RX and CTS lines of the CPU's UART (see [SER]).

When connecting a clock/data reader, wire the clock line to IO1, and the data line

to IO2. Set the CONTROL line to LOW -- this selects the clock/data mode for the

Tibbit's hardware.

When connecting a Wiegand reader, wire the W0 line to IO1, W1 line -- to IO2. Set

the CONTROL line to HIGH to select the Wiegand mode.

Most card readers with clock/data and Wiegand interfaces have open collector

outputs. Such outputs require pull-up resistors on the receiving end. On this Tibbit,

the role of pull-up resistors is played by opto-LEDs and resistors connected in

Loading...

Loading...