Master-slave coupling

In the event of an acve master/slave coupling (e. g. synchronism or cam proler applicaon),

the speed is not reduced automacally in the default seng. The automac speed reducon

is generally realised via the master axis.

Automac speed

reducon is acvated via the Follower - Response to SLS parameter.

40x500A:160

If automac speed reducon is acvated, the cyclically specied setpoint values are reduced

to the limited speed. The synchronism of the master axis is no longer guaranteed.

An oset occurring between master and slave is automacally resolved by deacvang the

parameter.40x500A:159

An excessive rotaonal speed due to following error compensaon is avoided by liming the

setpoint values at the speed regulator input. 40x500A:161

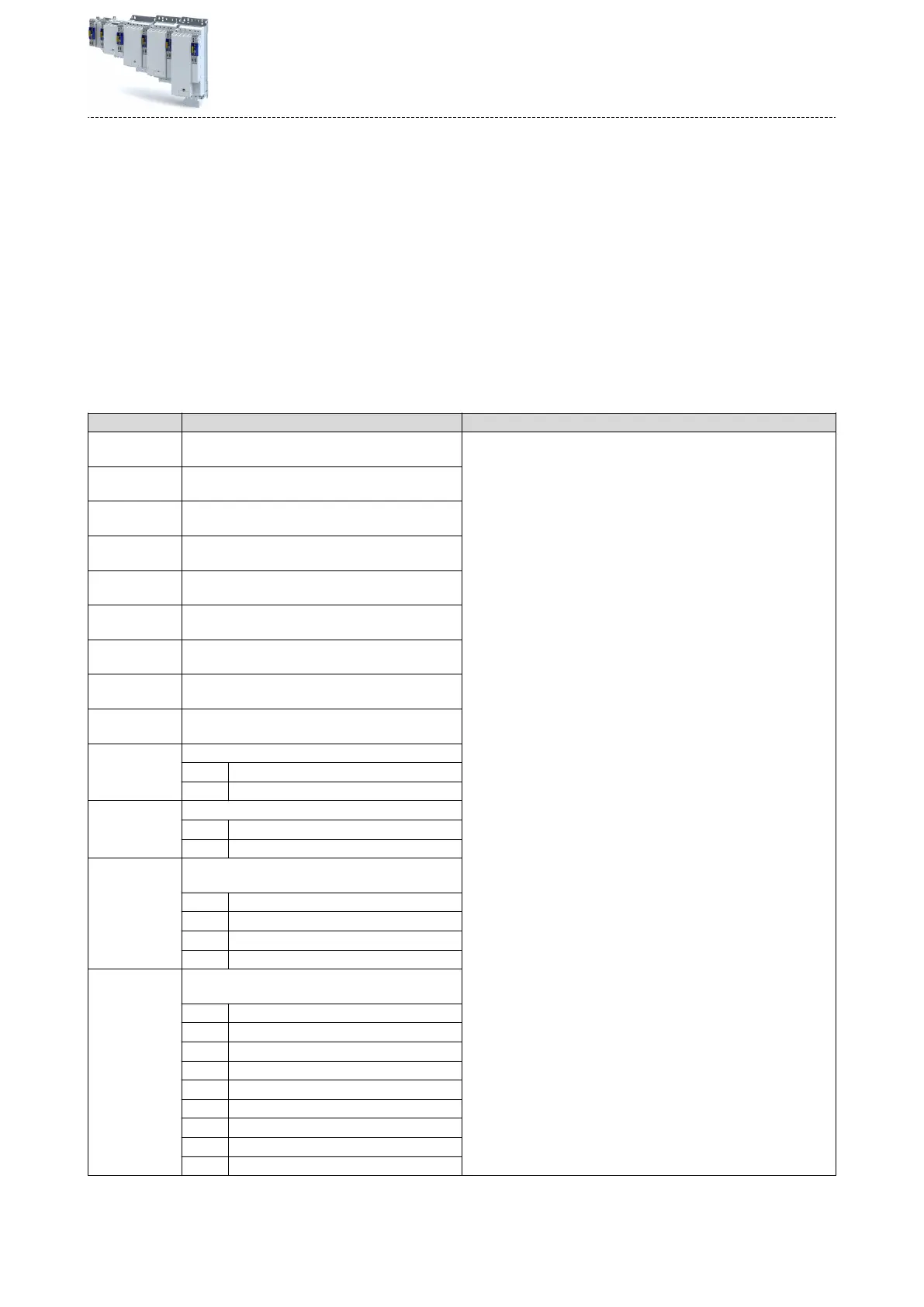

Parameter

Address Name / seng range / [default seng] Info

0x500A:150 SLS1

0.0000 ... [0.0000] ... 214748.3647

0x500A:151 SLS1 - deceleraon

me

0.000 ... [0.000] ... 2147483.647 s

0x500A:152 SLS2

0.0000 ... [0.0000] ... 214748.3647

0x500A:153 SLS2 - deceleraon me

0.000 ... [0.000] ... 2147483.647 s

0x500A:154 SLS3

0.0000 ... [0.0000] ... 214748.3647

0x500A:155 SLS3 - deceleraon me

0.000 ... [0.000] ... 2147483.647 s

0x500A:156 SLS4

0.0000 ... [0.0000] ... 214748.3647

0x500A:157 SLS4 - deceleraon me

0.000 ... [0.000] ... 2147483.647 s

0x500A:159 Compensaon velocity of SLS

0.0000 ... [0.0000] ... 214748.3647

0x500A:160 Follower - Response to SLS

false Inacve

true Acve

0x500A:161 Speed controller limitaon (SLS)

false Inacve

true Acve

0x500A:162 Deacvate safety funcons

0x00000000 ... [0x00000000] ... 0xFFFFFFFF

Bit 1 Ignore SS1 request

Bit 2 Ignore SS2 request

Bit 3 Ignore SLS1-4 request

Bit 4 Ignore SDI request

0x500A:163 Limiter status

•

R

ead only

Bit 0 STO acve

Bit 1 SS1 acve

Bit 2 SS2 acve

Bit 4 SLS1 acve

Bit 5 SLS2 acve

Bit 6 SLS3 acve

Bit 7 SLS4 acve

Bit 8 SDIpos acve

Bit 9 SDIneg acve

Technology applicaon (TA) basic sengs

Moon sengs

Limitaons

77

Loading...

Loading...