4.5

Date Code 20130214 Instruction Manual SEL-2414 Transformer Monitor

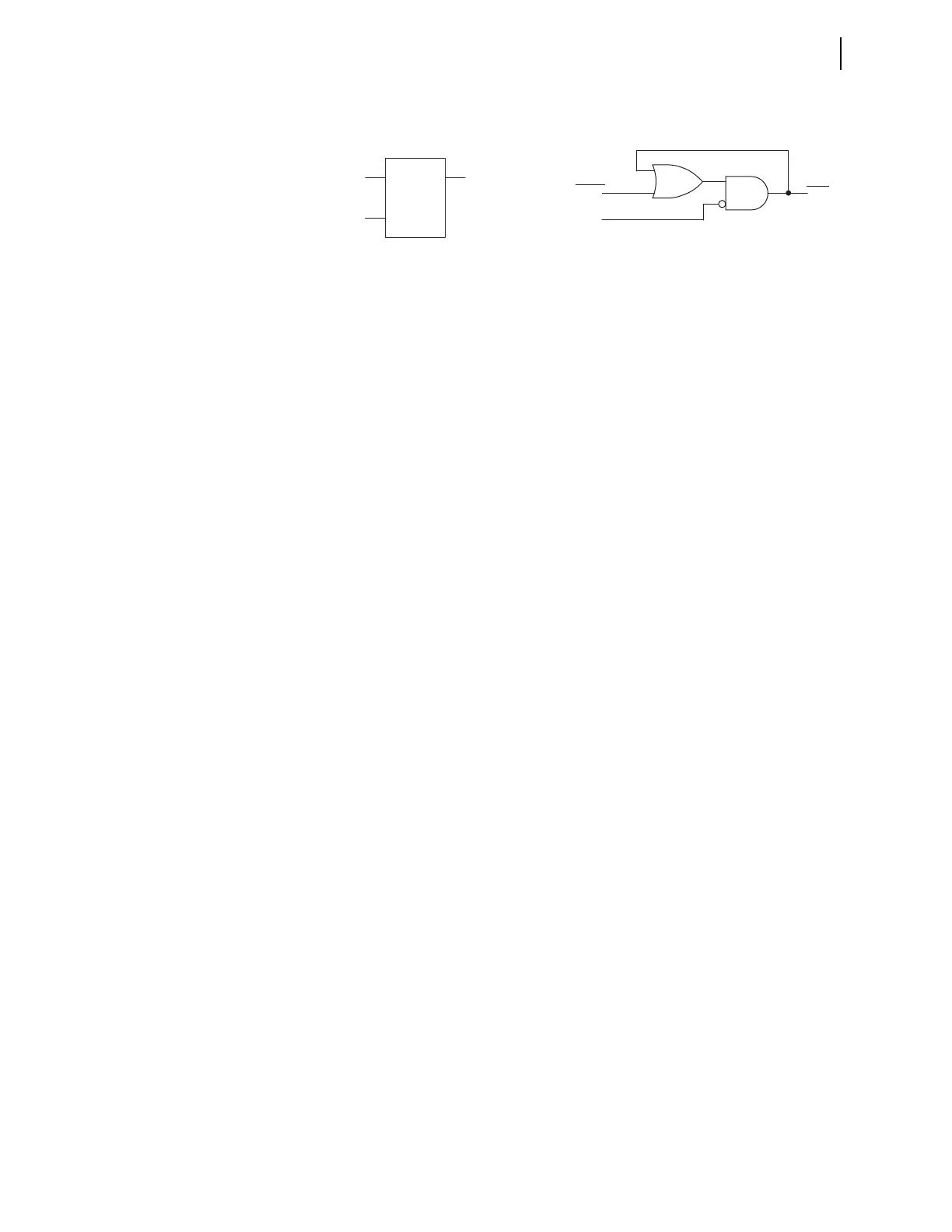

Logic Functions

General Logic Functions

If setting SETn asserts to logical 1, latch bit LTn asserts to logical 1. If setting

RSTn asserts to logical 1, latch bit LTn deasserts to logical 0. If both settings

SETn and RSTn assert to logical 1, setting RSTn has priority and latch bit LTn

deasserts to logical 0. The SET and RESET default settings are NA.

Power Loss

The states of the latches (LT01–LT32) are retained if power to the device is lost

and then restored. If a latch is asserted when power is lost, it is asserted when

power is restored. If a latch is deasserted when power is lost, it is deasserted

when power is restored.

Settings Change

If individual settings are changed, the states of the latches are retained, as in the

preceding Power Loss explanation. If an individual setting change causes a

change in SEL

OGIC control equation setting SETn or RSTn, the retained states of

the latch bits can be changed, subject to the newly enabled settings SETn or

RSTn.

Latch Settings

Latch states are stored in battery-backed RTC SRAM. An operational battery in

the Real Time Clock is necessary to ensure that Latch settings are not compro-

mised.

Settings SETn and RSTn cannot result in continuous cyclical operation of latch

bit LTn. Use timers to qualify conditions set in settings SETn and RSTn. If you

use any optoisolated inputs in settings SETn and RSTn, the inputs each have a

separate debounce timer that can help in providing the necessary time qualifica-

tion.

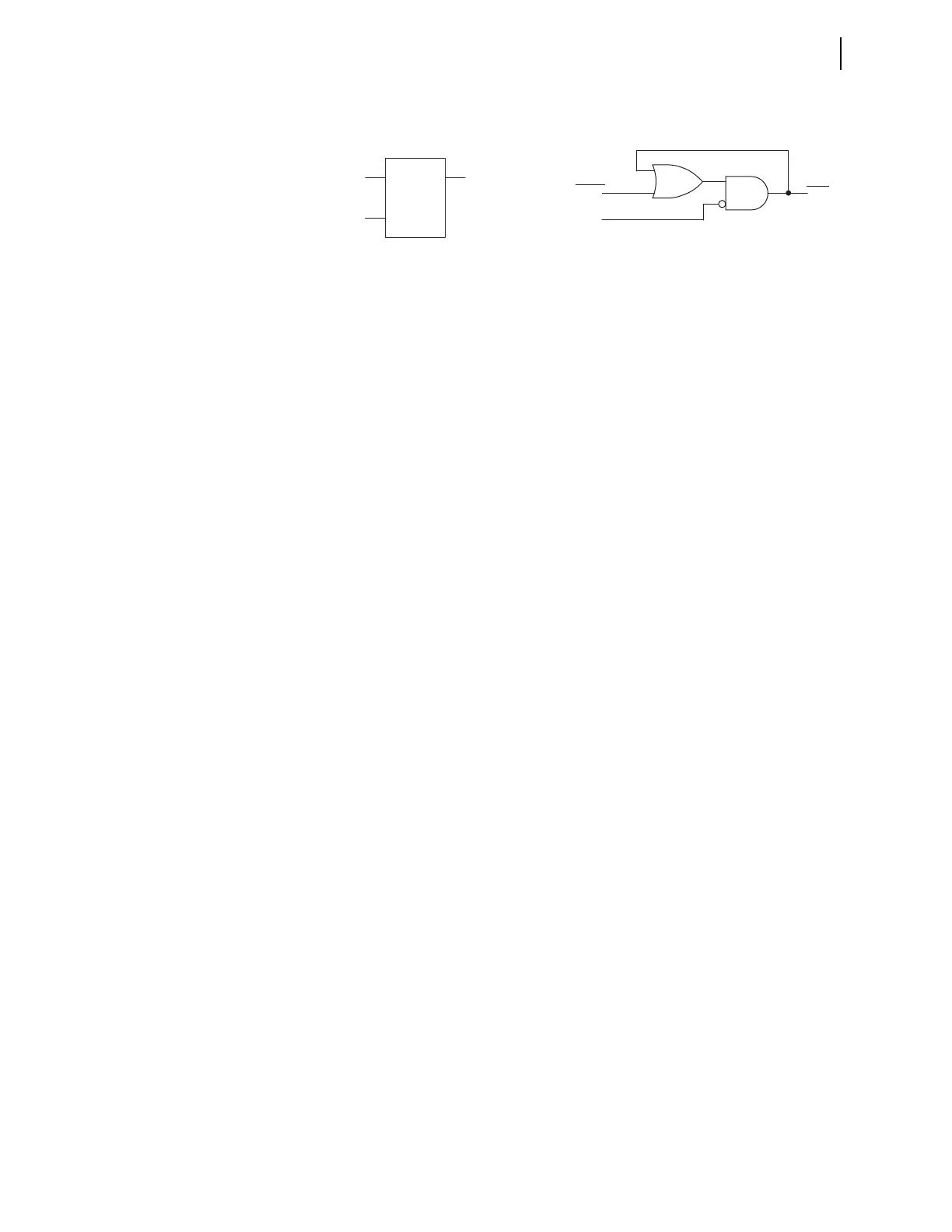

Variables/Timers

Operation

Each SELOGIC control equation variable/timer has a SELOGIC control equation

setting input and variable/timer outputs as shown in Figure 4.6. Timers SV01T

through SV64T in Figure 4.6 have a setting range of 0.000–16000.00 seconds.

This timer setting range applies to both pickup and dropout times (SvnPU and

SVnDO, n = 1 through 64).

Figure 4.5 Logic Diagram of a Latch Switch

LT01

R

Q

S

SET01

RST01

IEC 61131-3 Latch

(b)(a)

LTn

SETn

RSTn

(Set)

(Reset)

(n = 01 through 32)

Device

Word

Bits

SELOGIC

Setting

Loading...

Loading...