RL78/G10 CHAPTER 6 TIMER ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 119

Dec 22, 2016

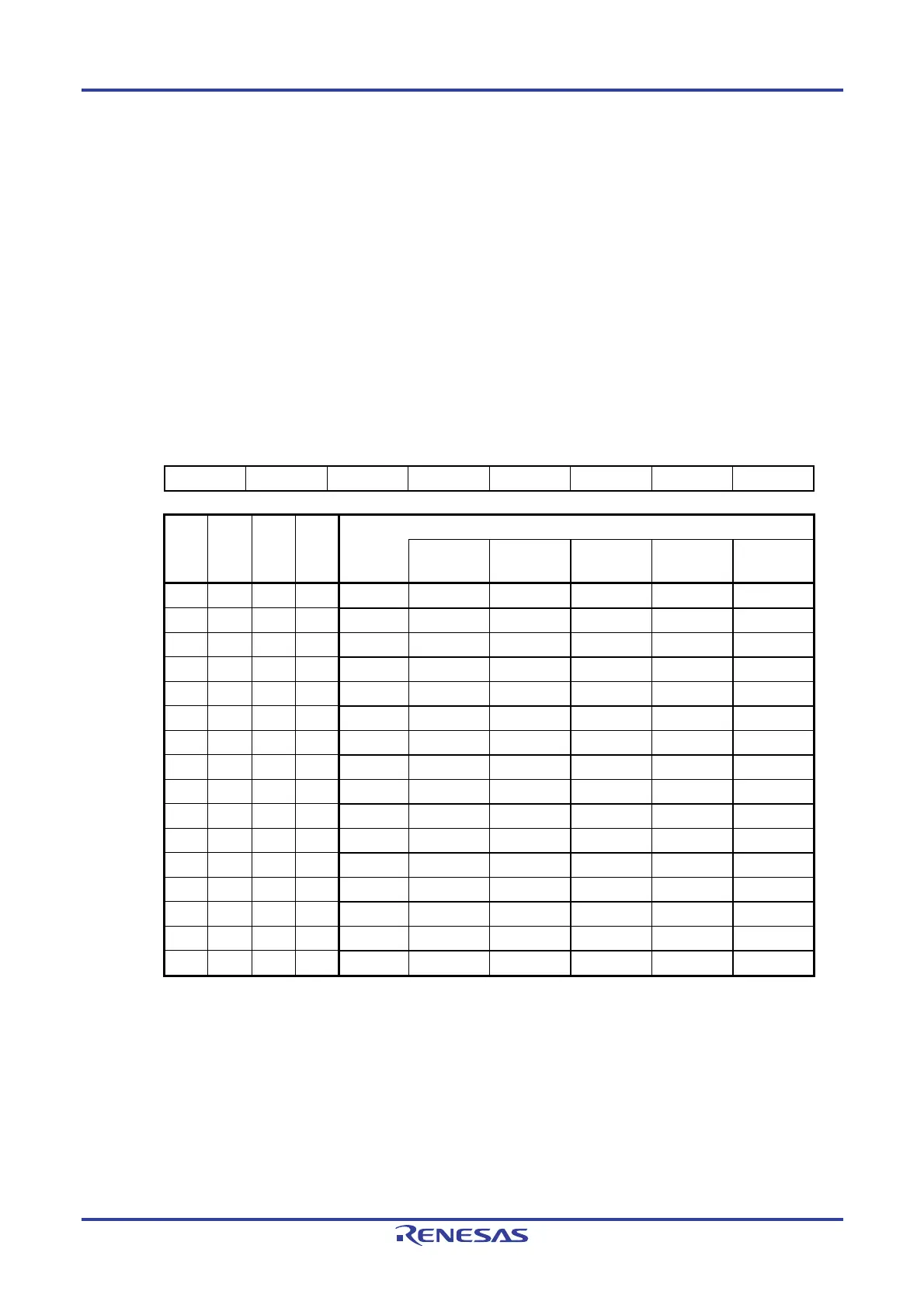

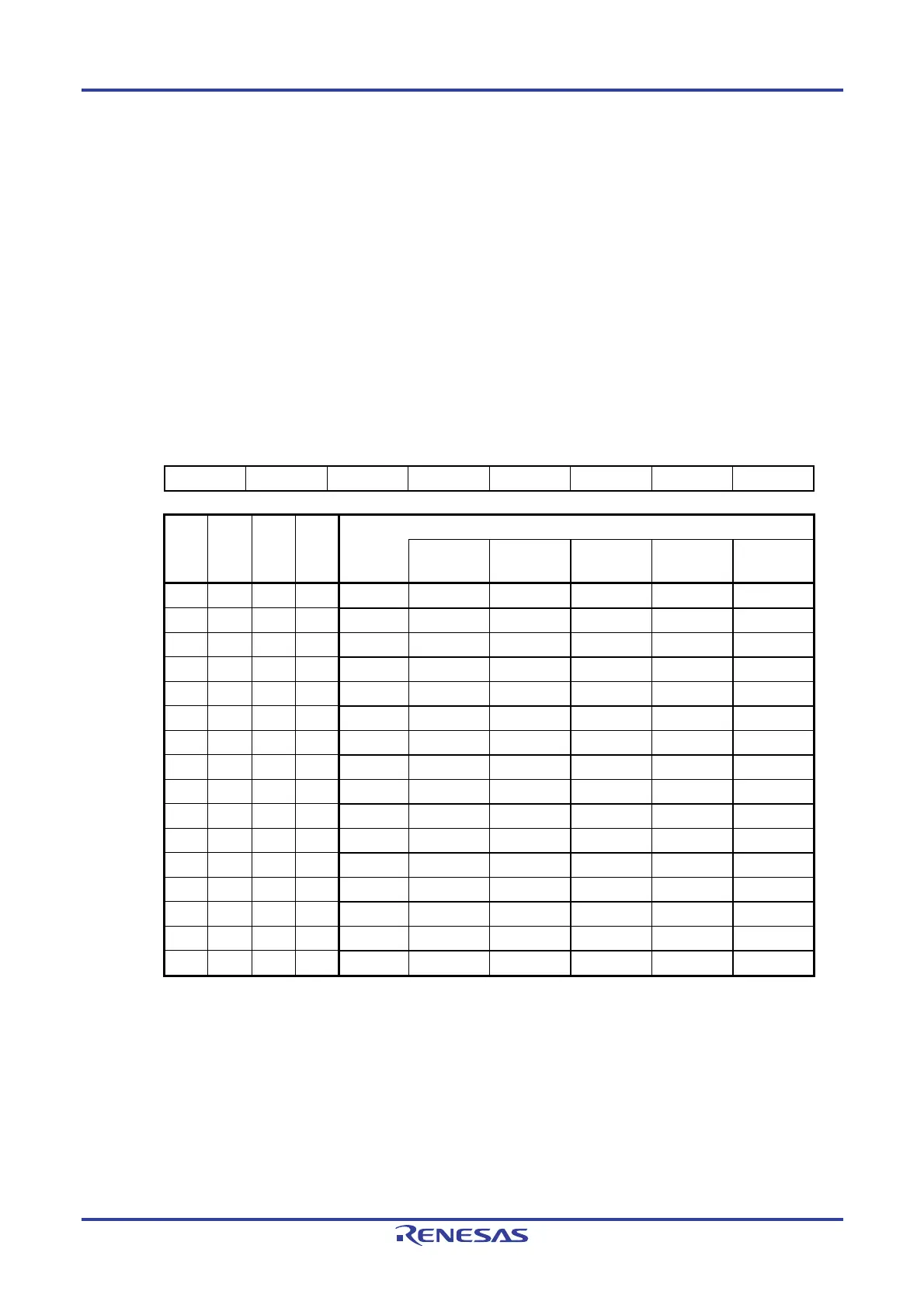

6.3.2 Timer clock select register 0 (TPS0)

The TPS0 register is a 16-bit register that is used to select four types of operation clocks (CK00, CK01) that are

commonly supplied to each channel from the prescaler.

Rewriting of the TPS0 register during timer operation is possible only in the following cases.

If the PRS000 to PRS003 bits can be rewritten (n = 0 to 3):

All channels for which CK00 is selected as the operation clock (CKS0n1 = 0) are stopped (TE0n = 0).

If the PRS010 to PRS013 bits can be rewritten (n = 0 to 3):

All channels for which CK01 is selected as the operation clock (CKS0n1 = 1) are stopped (TE0n = 0).

The TPS0 register can be set by a 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

Figure 6-7. Format of Timer Clock Select Register 0 (TPS0)

Address: F01B6H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

TPS0 PRS013 PRS012 PRS011 PRS010 PRS003 PRS002 PRS001 PRS000

PRS

0k3

PRS

0k2

PRS

0k1

PRS

0k0

Selection of operation clock (CK0k)

Note

(k = 0, 1)

f

CLK =

1.25 MHz

fCLK =

2.5 MHz

f

CLK =

5 MHz

f

CLK =

10 MHz

f

CLK =

20 MHz

0 0 0 0 fCLK

1.25 MHz 2.5 MHz 5 MHz 10 MHz 20 MHz

0 0 0 1 fCLK/2

625 kHz 1.25 MHz 2.5 MHz 5 MHz 10 MHz

0 0 1 0 fCLK/2

2

313 kHz 625 kHz 1.25 MHz 2.5 MHz 5 MHz

0 0 1 1 fCLK/2

3

156 kHz 313 kHz 625 kHz 1.25 MHz 2.5 MHz

0 1 0 0 fCLK/2

4

78.1 kHz 156 kHz 313 kHz 625 kHz 1.25 MHz

0 1 0 1 fCLK/2

5

39.1 kHz 78.1 kHz 156 kHz 313 kHz 625 kHz

0 1 1 0 fCLK/2

6

19.5 kHz 39.1 kHz 78.1 kHz 156 kHz 313 kHz

0 1 1 1 fCLK/2

7

9.77 kHz 19.5 kHz 39.1 kHz 78.1 kHz 156 kHz

1 0 0 0 fCLK/2

8

4.88 kHz 9.77 kHz 19.5 kHz 39.1 kHz 78.1 kHz

1 0 0 1 fCLK/2

9

2.44 kHz 4.88 kHz 9.77 kHz 19.5 kHz 39.1 kHz

1 0 1 0 fCLK/2

10

1.22 kHz 2.44 kHz 4.88 kHz 9.77 kHz 19.5 kHz

1 0 1 1 fCLK/2

11

610 Hz 1.22 kHz 2.44 kHz 4.88 kHz 9.77 kHz

1 1 0 0 fCLK/2

12

305 Hz 610 Hz 1.22 kHz 2.44 kHz 4.88 kHz

1 1 0 1 fCLK/2

13

153 Hz 305 Hz 610 Hz 1.22 kHz 2.44 kHz

1 1 1 0 fCLK/2

14

76.3 Hz 153 Hz 305 Hz 610 Hz 1.22 kHz

1 1 1 1 fCLK/2

15

38.1 Hz 76.3 Hz 153 Hz 305 Hz 610 Hz

Note When changing the clock selected for f

CLK (by changing the system clock control register (CKC)

value), stop timer array unit (TT0 = 0FH, TTH0 = 0AH).

Caution If f

CLK (undivided) is selected as the operation clock (CK0k) and TDR0nH and TDR0nL are

cleared to 00H (n = 0 to 3), the interrupt request signal (INTTM0n) output from timer array

units cannot be used.

Remarks 1. f

CLK: CPU/peripheral hardware clock frequency

2. The above selected clock, but a signal which becomes high level for one f

CLK cycle period from

its rising edge. For details, see 6.5.1 Count clock (f

TCLK).

Loading...

Loading...