RL78/G10 CHAPTER 17 RESET FUNCTION

R01UH0384EJ0311 Rev. 3.11 535

Dec 22, 2016

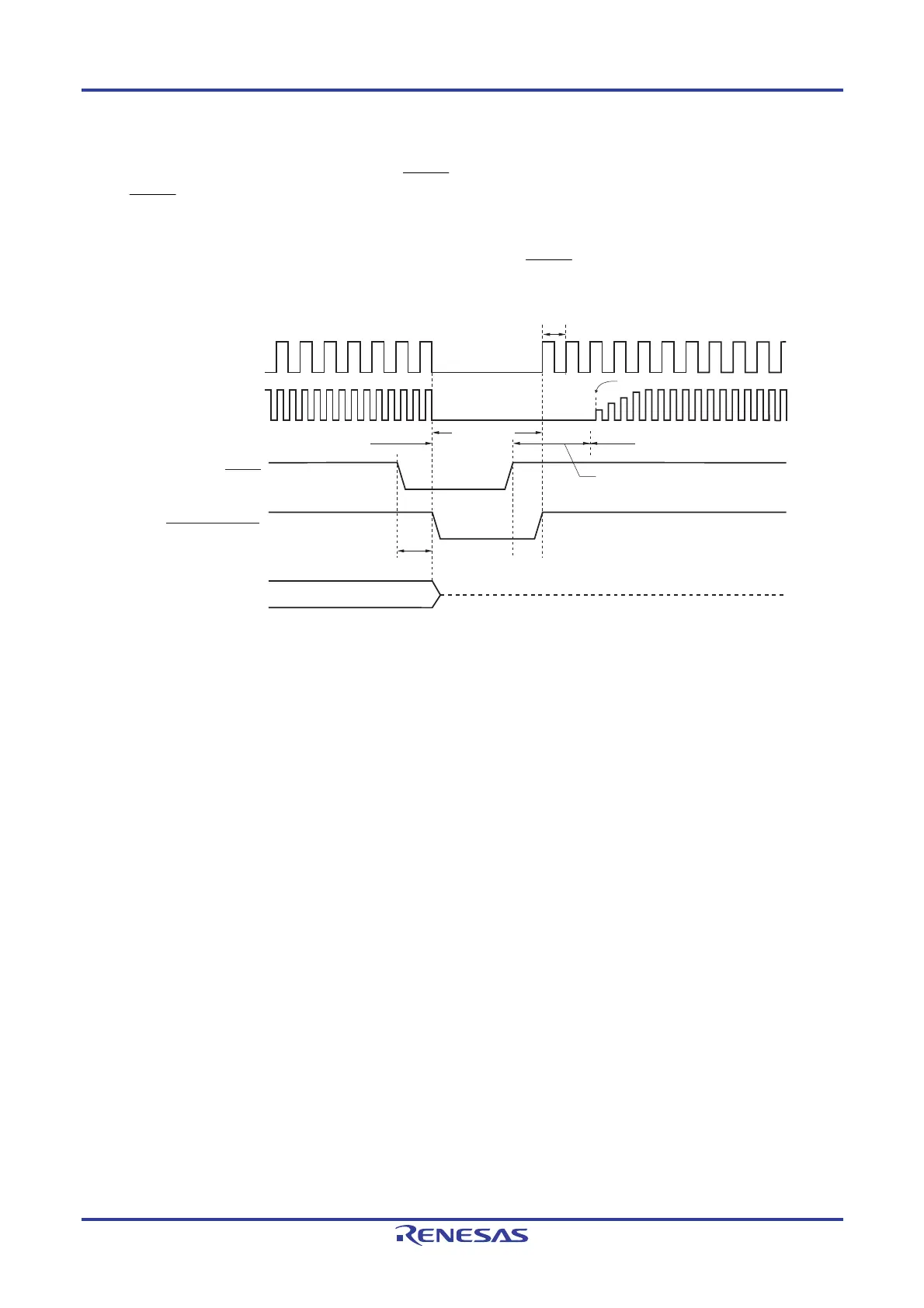

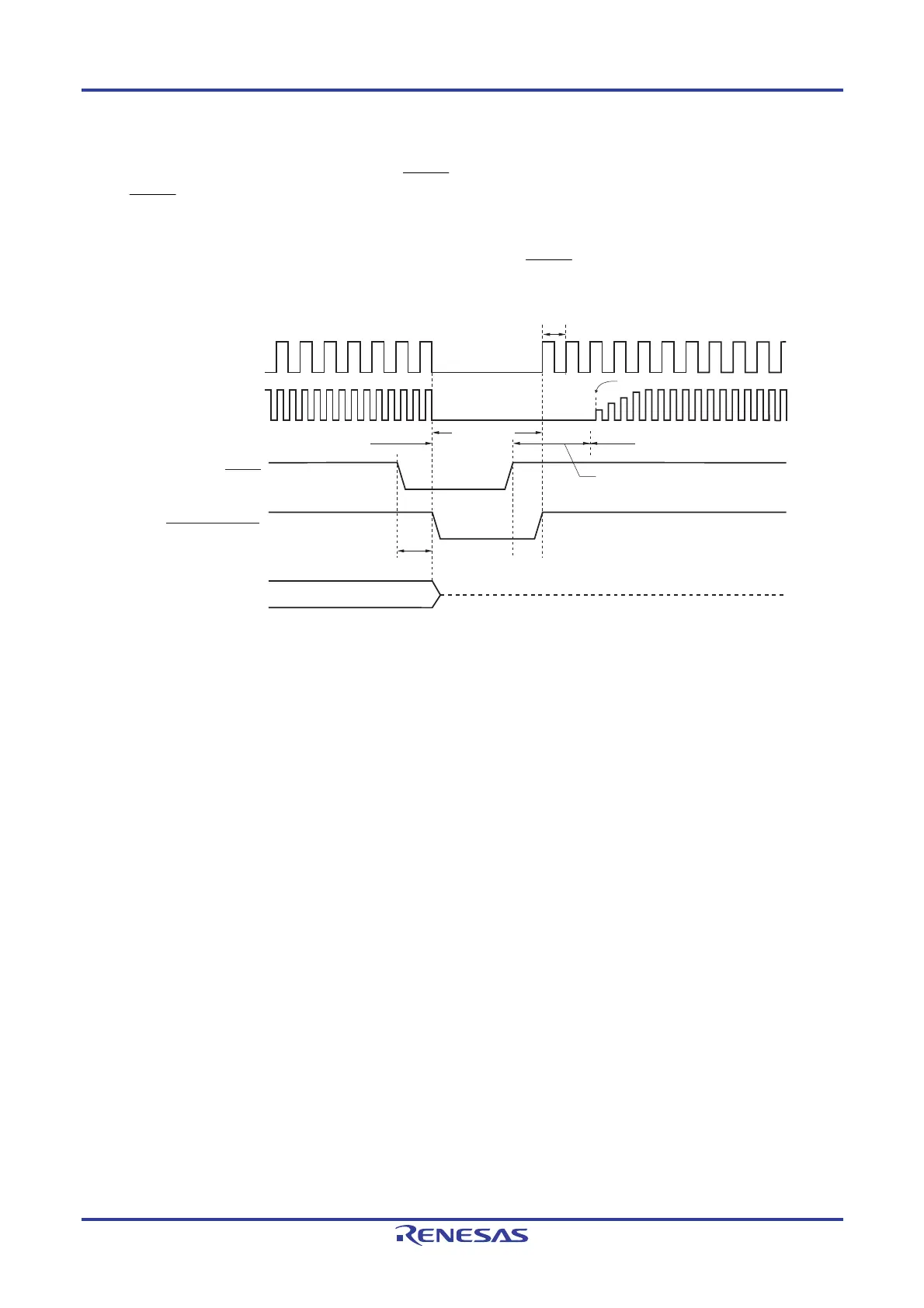

17.1 Timing of Reset Operation

This LSI is reset by input of the low level on the RESET pin and released from the reset state by input of the high level

on the RESET pin. After reset processing, execution of the program with the high-speed on-chip oscillator clock as the

operating clock starts.

Figure 17-2. Timing of Reset by RESET Input

Delay

Hi-Z

Note 3

Normal operationCPU status

Normal operation

(high-speed on-chip oscillator clock)

RESET

Internal reset signal

Port pin

High-speed system clock

(when X1 oscillation is selected)

Note 1

High-speed on-chip

oscillator clock

Starting X1 oscillation is specified by software.

Reset processing for release from the

external reset state: 500

µ

s (typ.)

Note 2

Wait for oscillation

accuracy stabilization

Reset period

(oscillation

stop)

Notes 1. 16-pin products only.

2. After power is supplied, an SPOR reset processing time of (MAX. 3.01 ms) is required before reset

processing starts after release of the external reset.

3. Status of port pin P40 is as follows.

• High-impedance during external reset period or reset period by the data retention power supply voltage

• High level after receiving a reset (connected to the internal pull-up resistor)

Loading...

Loading...