RL78/G10 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 306

Dec 22, 2016

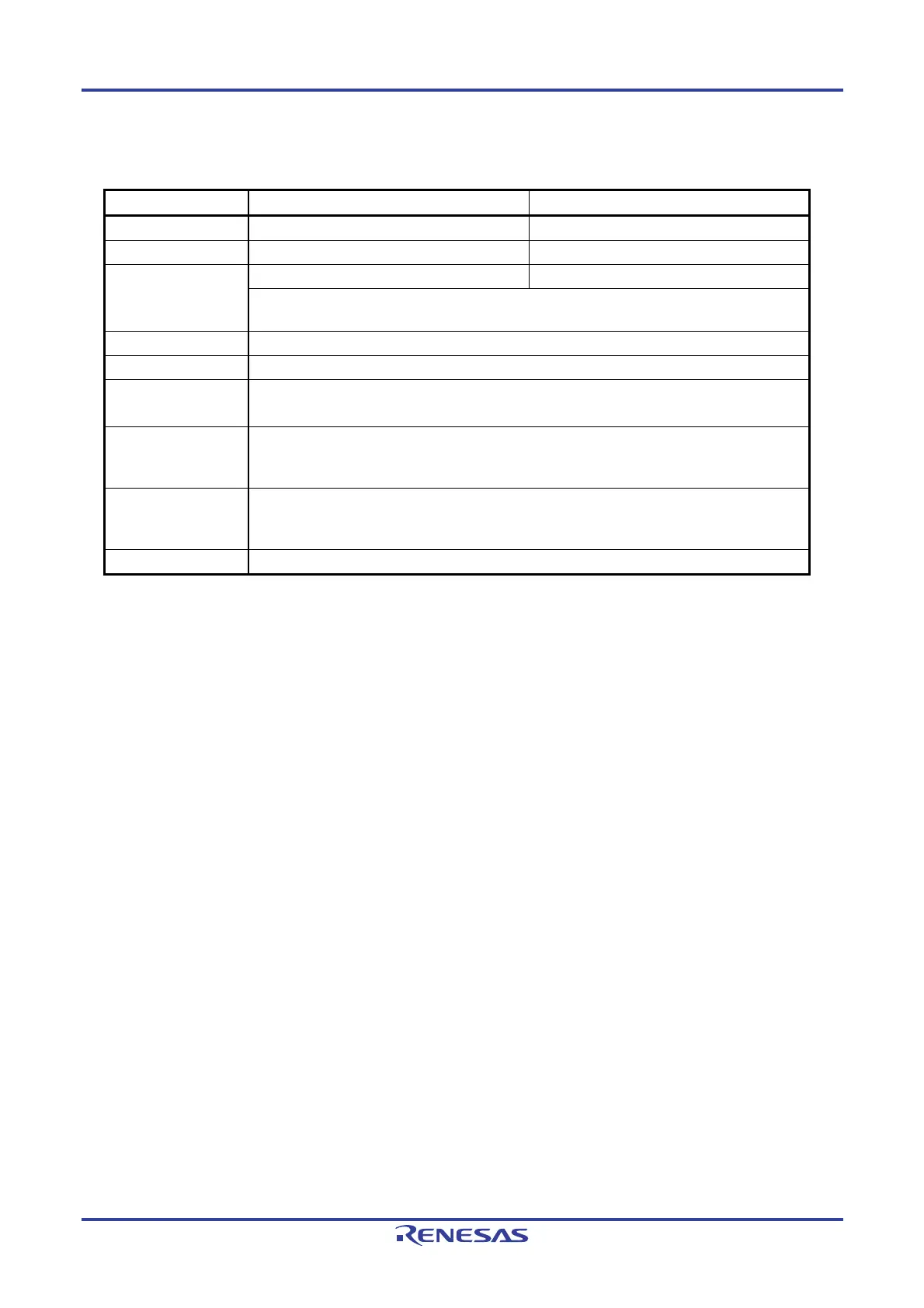

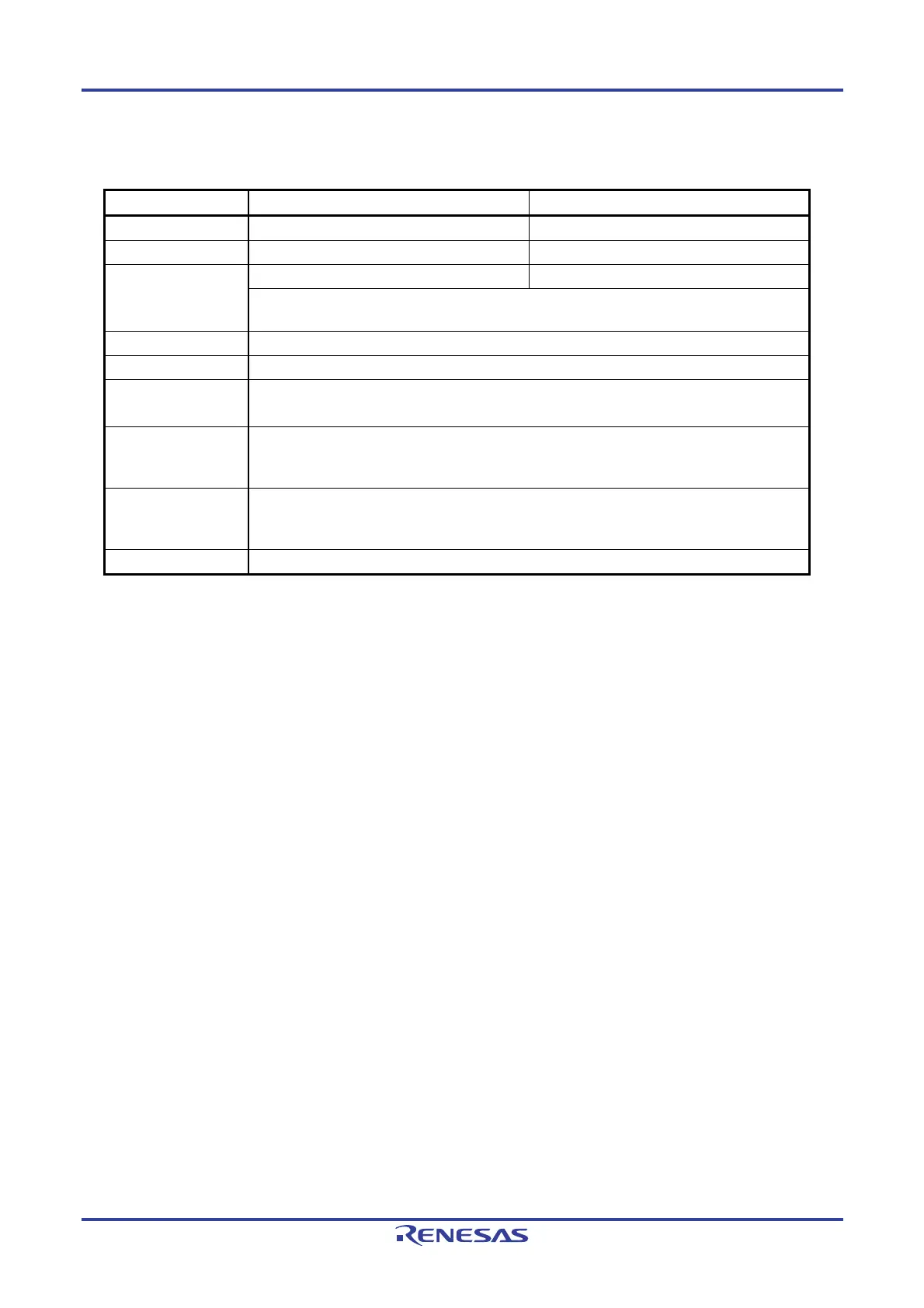

12.5.1 Master transmission

Master transmission is that the RL78/G10 outputs a transfer clock and transmits data to another device.

3-Wire Serial I/O CSI00 CSI01

Note 1

Target channel Channel 0 of SAU0 Channel 1 of SAU0

Pins used SCK00, SO00 SCK01, SO01

Interrupt INTCSI00 INTCSI01

Transfer end interrupt (in single-transfer mode) or buffer empty interrupt (in continuous transfer

mode) can be selected.

Error detection flag None

Transfer data length 7 or 8 bits

Transfer rate

Note 2

Max. fCLK/4 [Hz] (SDR0nH[7:1] = 1 or more)

Min. f

CLK/(2 × 2

15

× 128) [Hz]

Data phase

Selectable by the DAP0n bit of the SCR0nH register

• DAP0n = 0: Data output starts at the start of the operation of the serial clock.

• DAP0n = 1: Data output starts half a clock before the start of the serial clock operation.

Clock phase

Selectable by the CKP0n bit of the SCR0nH register

• CKP0n = 0: Non-reverse (data output at the falling edge and data input at the rising edge of SCK)

• CKP0n = 1: Reverse (data output at the rising edge and data input at the falling edge of SCK)

Data direction MSB or LSB first

Notes 1. 16-pin products only.

2. Use this operation within a range that satisfies the conditions above and the peripheral function

characteristics in the electrical specifications (see CHAPTER 24 ELECTRICAL SPECIFICATIONS).

Remarks 1. fCLK: System clock frequency

2. n = 0, 1

Loading...

Loading...