RL78/G10 CHAPTER 3 CPU ARCHITECTURE

R01UH0384EJ0311 Rev. 3.11 43

Dec 22, 2016

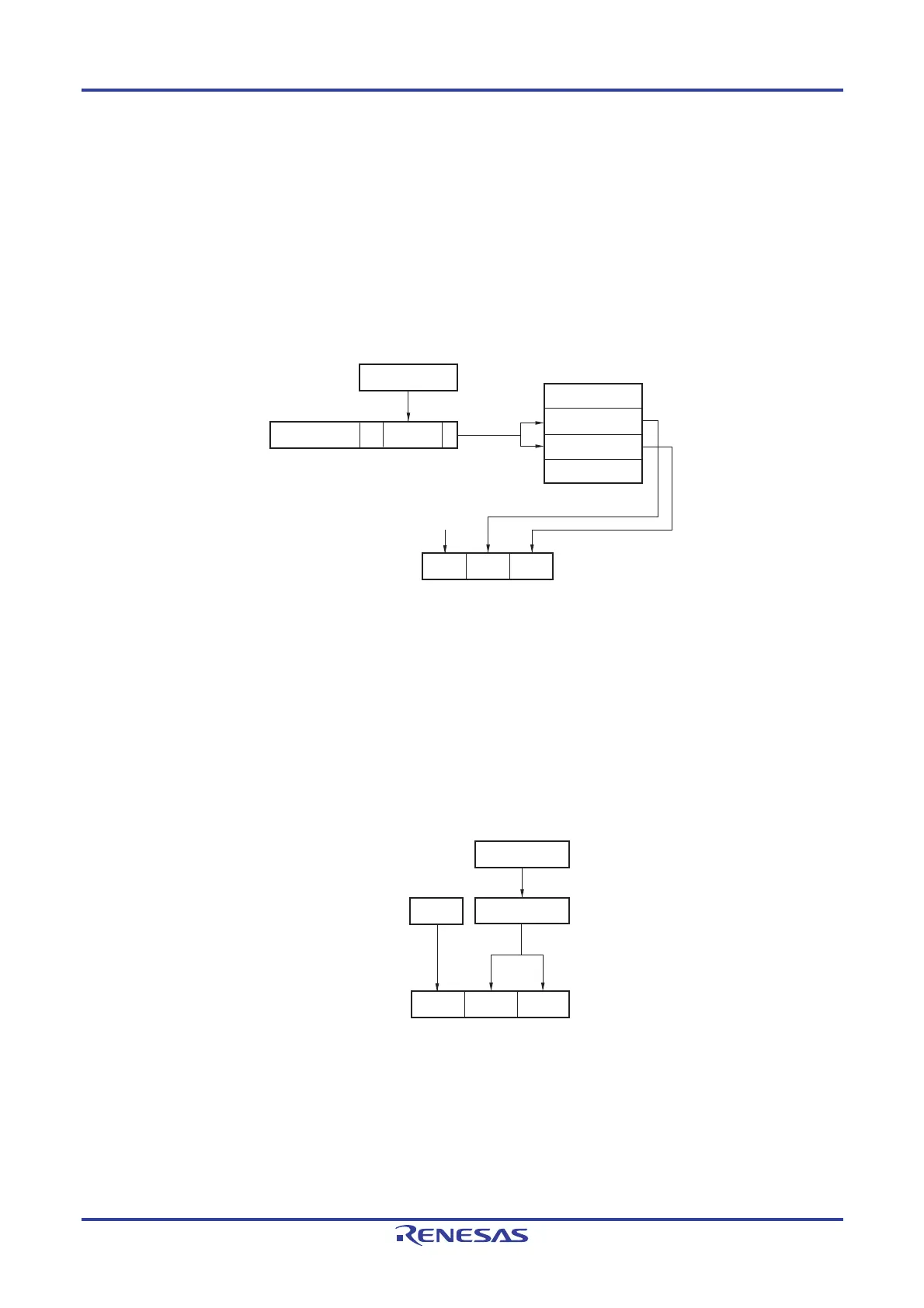

3.3.3 Table indirect addressing

[Function]

Table indirect addressing specifies a table address in the CALLT table area (0080H to 00BFH) with the 5-bit

immediate data in the instruction word, stores the contents at that table address and the next address in the program

counter (PC) as 16-bit data, and specifies the program address. Table indirect addressing is applied only for CALLT

instructions.

In the RL78 microcontrollers, branching is enabled only to the 64 KB space from 00000H to 0FFFFH.

Figure 3-14. Outline of Table Indirect Addressing

Low Addr.

High Addr.

0

0000

OP code

00000000 10

Table address

PC

S

PC PC

H

PC

L

Memory

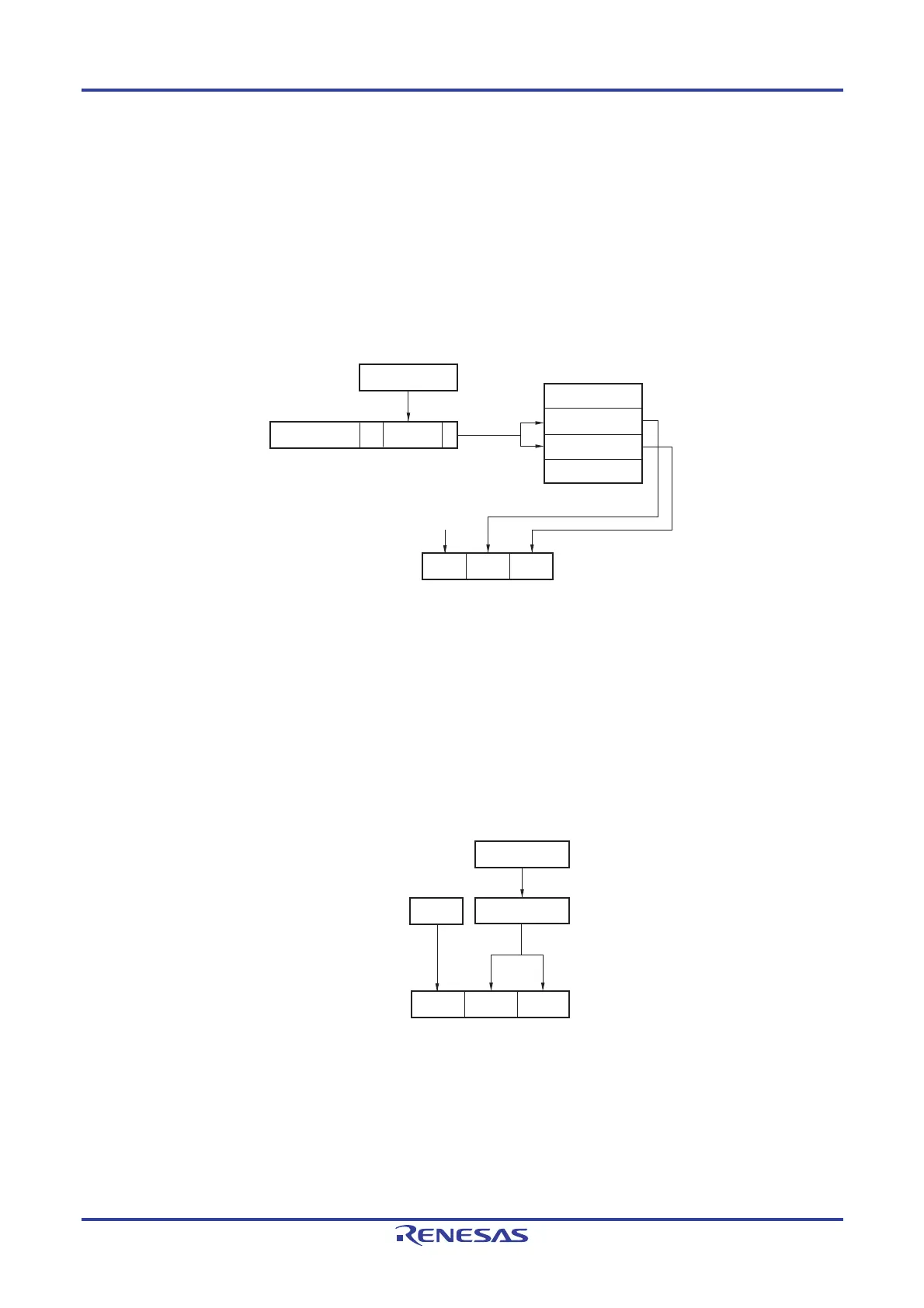

3.3.4 Register direct addressing

[Function]

Register direct addressing stores in the program counter (PC) the contents of a general-purpose register pair

(AX/BC/DE/HL) and CS register of the current register bank specified with the instruction word as 20-bit data, and

specifies the program address. Register direct addressing can be applied only to the CALL AX, BC, DE, HL, and BR

AX instructions.

Figure 3-15. Outline of Register Direct Addressing

OP code

PC

S

PC

PC

H

PC

L

CS

rp

Instruction code

Loading...

Loading...