RL78/G10 CHAPTER 6 TIMER ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 131

Dec 22, 2016

6.3.10 Timer output level register 0 (TOL0)

The TOL0 register is a register that controls the timer output level of each channel.

The setting of the inverted output of channel n by this register is reflected at the timing of set or reset of the timer output

signal while the timer output is enabled (TOE0n = 1) in the Slave channel output mode (TOM0n = 1). In the master

channel output mode (TOM0n = 0), this register setting is invalid.

The TOL0 register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

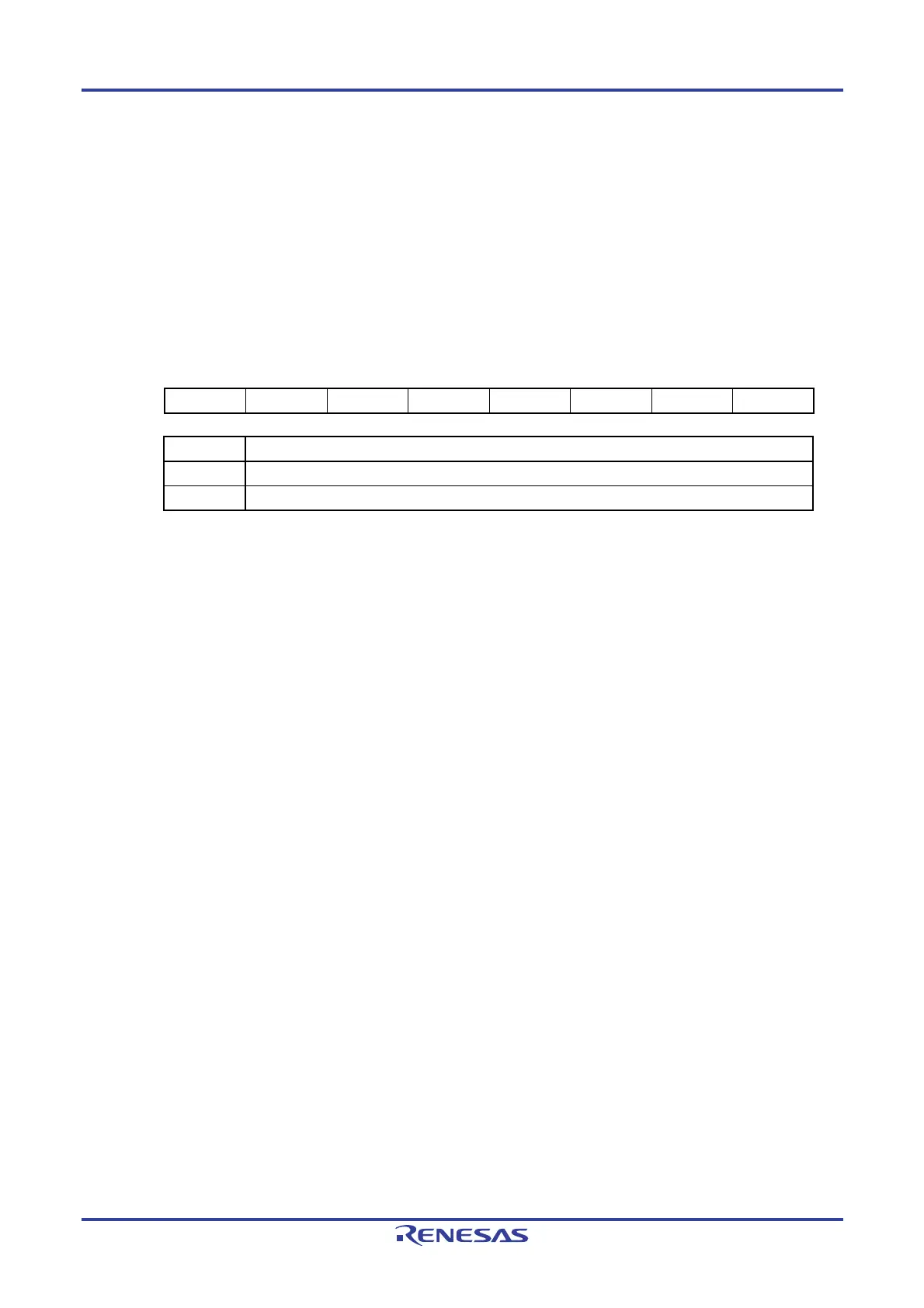

Figure 6-18. Format of Timer Output Level Register 0 (TOL0)

Address: F01BCH After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

TOL0 0 0 0 0 TOL03

Note

TOL02

Note

TOL01 0

TOL0n Control of timer output level of channel n

0 Positive logic output (active-high)

1 Negative logic output (active-low)

Note 16-pin products only.

Caution Be sure to clear bits 0, 2 to 7 in 10-pin products and bits 0, 4 to 7 in 16-pin products to 0.

Remarks 1. The timer output logic is inverted when the timer output signal changes next, instead of

immediately after the TOL0 register value is rewritten.

2. n: Channel number

n = 0, 1 (for 10-pin products); n = 0 to 3 (for 16-pin products)

Loading...

Loading...