RL78/G10 CHAPTER 6 TIMER ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 132

Dec 22, 2016

6.3.11 Timer output mode register 0 (TOM0)

The TOM0 register is used to control the timer output mode of each channel.

When a channel is used for the independent channel operation function, set the corresponding bit of the channel to be

used to 0.

When a channel is used for the simultaneous channel operation function (one-shot pulse output, two-channel input with

one-shot pulse output function

Note

, PWM output, multiple PWM output

Note

), set the corresponding bit of the master

channel to 0 and the corresponding bit of the slave channel to 1.

The setting of each channel n by this register is reflected at the timing when the timer output signal is set or reset while

the timer output is enabled (TOE0n = 1).

The TOM0 register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

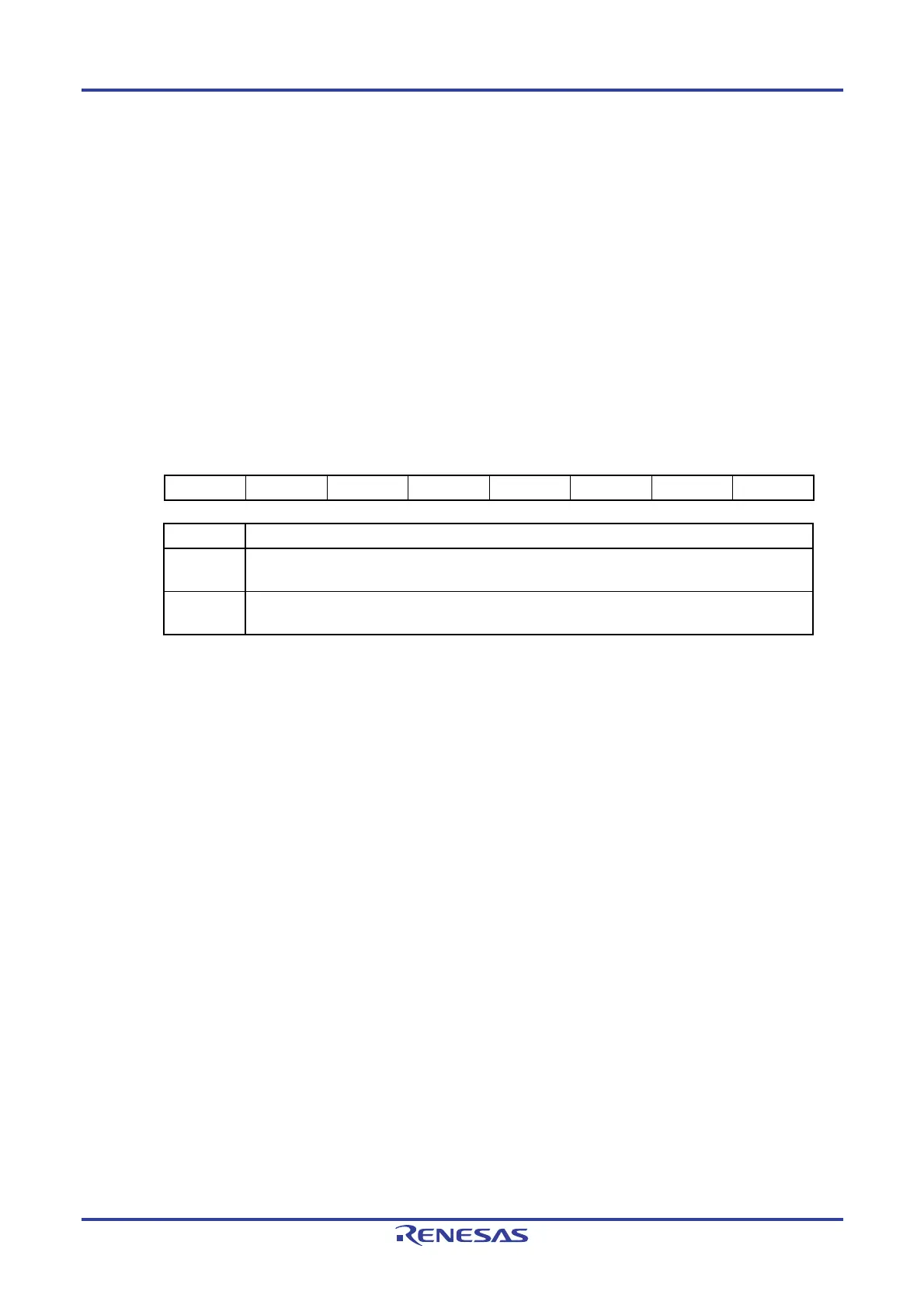

Figure 6-19. Format of Timer Output Mode Register 0 (TOM0)

Address: F01BEH After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

TOM0 0 0 0 0 TOM03

Note

TOM02

Note

TOM01 0

TOM0n Control of timer output mode of channel n

0

Used as the independent channel operation function (to produce toggle output by the interrupt

request signal (INTTM0n))

1

Slave channel output mode (output is set by the interrupt request signal (INTTM00, INTTM02) of the

master channel, and reset by the timer interrupt request signal (INTTM0p) of the slave channel)

Note 16-pin products only.

Caution Be sure to clear bits 0, 2 to 7 in 10-pin products and bits 0, 4 to 7 in 16-pin products to 0.

Remark n: Master channel number

n = 0 (for 10-pin products); n = 0, 2 (for 16-pin products)

p: Slave channel number

p = 1 (for 10-pin products); n < p ≤ 3 (for 16-pin products)

(For details of the relation between the master channel and slave channel, refer to 6.4.1 Basic

rules of simultaneous channel operation function.)

Loading...

Loading...