RL78/G10 CHAPTER 8 CLOCK OUTPUT/BUZZER OUTPUT CONTROLLER

R01UH0384EJ0311 Rev. 3.11 232

Dec 22, 2016

8.3.1 Clock output select register 0 (CKS0)

This register sets output enable/disable for clock output or for the buzzer frequency output pin (PCLBUZ0), and sets the

output clock.

The CKS0 register is set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

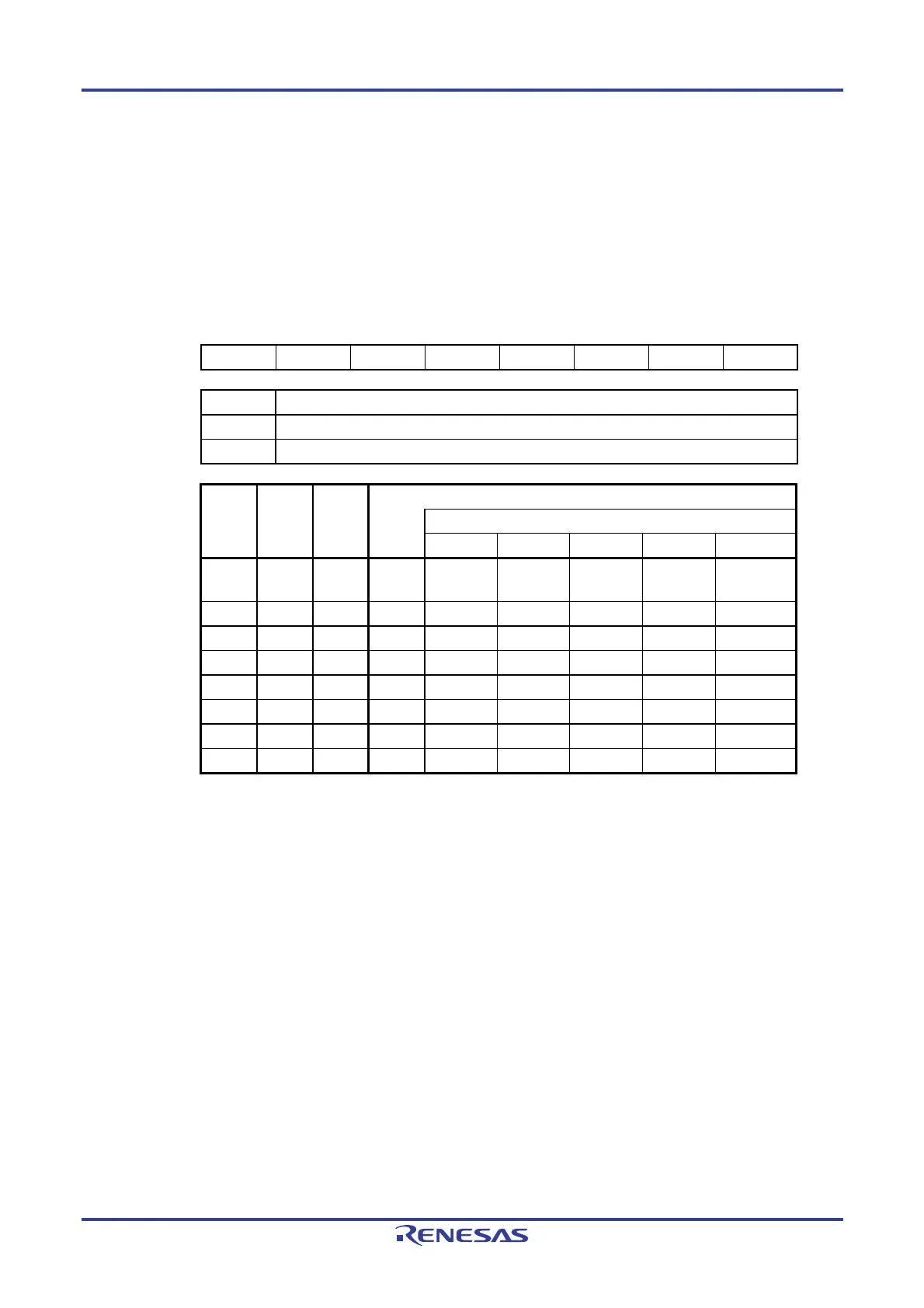

Figure 8-2. Format of Clock Output Select Register 0 (CKS0)

Address: FFFA5H After reset: 00H R/W

Symbol <7> 6 5 4 3 2 1 0

CKS0 PCLOE0 0 0 0 0 CCS02 CCS01 CCS00

PCLOE0 PCLBUZ0 pin output enable/disable specification

0 Output disable (default)

1 Output enable

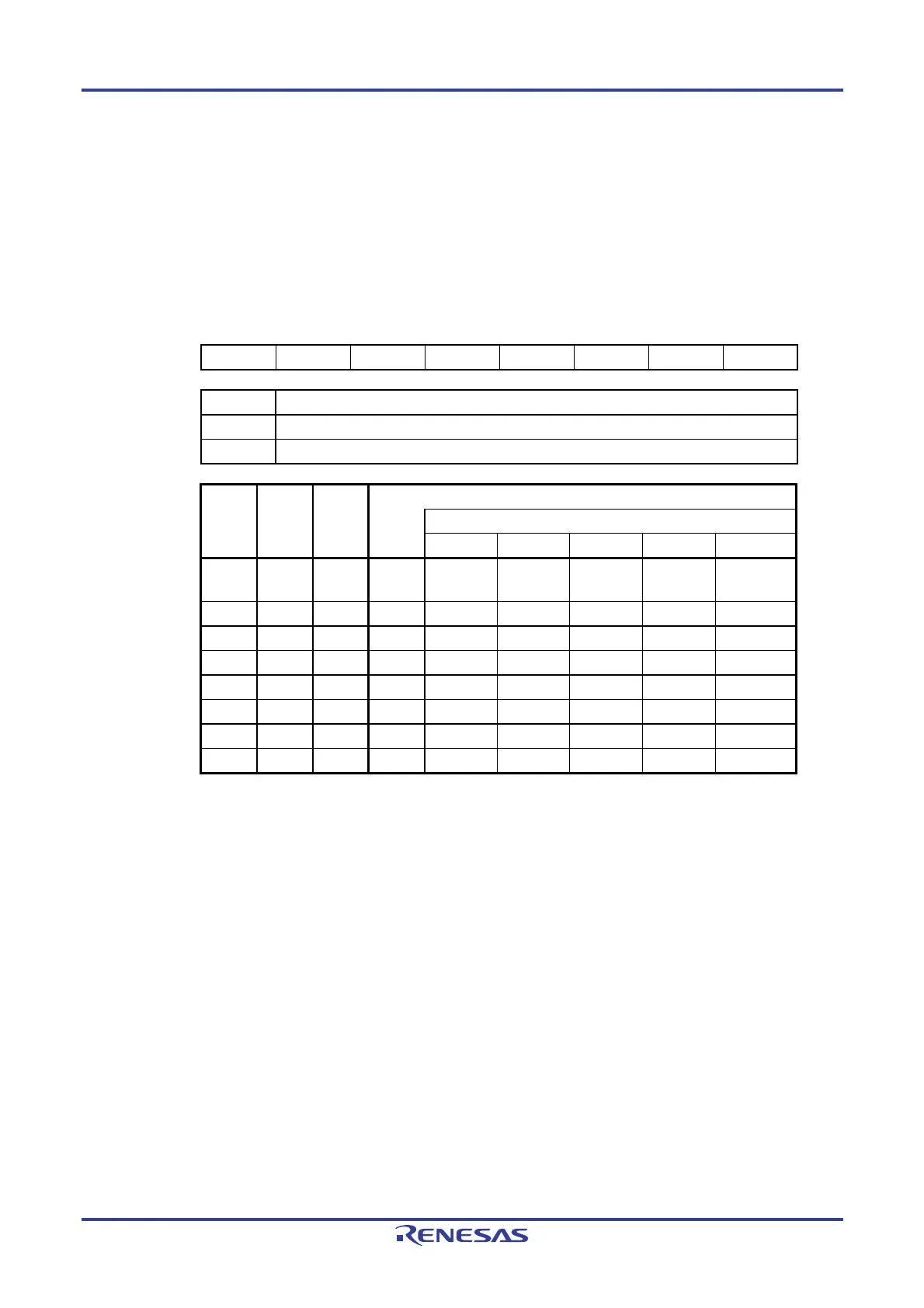

CCS02 CCS01 CCS00 PCLBUZ0 pin output clock selection

fMAIN (MHz)

1.25 2.5 5 10 20

0 0 0 fMAIN 1.25 MHz 2.5 MHz 5 MHz

Note

10 MHz

Note

Setting

prohibited

Note

0 0 1 fMAIN/2 625 kHz 1.25 MHz 2.5 MHz 5 MHz

Note

10 MHz

Note

0 1 0 fMAIN/2

2

312.5 kHz 625 kHz 1.25 MHz 2.5 MHz 5 MHz

Note

0 1 1 fMAIN/2

3

156.3 kHz 312.5 kHz 625 kHz 1.25 MHz 2.5 MHz

1 0 0 fMAIN/2

4

78.1 kHz 156.3 kHz 312.5 kHz 625 kHz 1.25 MHz

1 0 1 fMAIN/2

11

610 Hz 1.22 kHz 2.44 kHz 4.88 kHz 9.77 kHz

1 1 0 fMAIN/2

12

305 Hz 610 Hz 1.22 kHz 2.44 kHz 4.88 kHz

1 1 1 fMAIN/2

13

153 Hz 305 Hz 610 Hz 1.22 kHz 2.44 kHz

Note The available output clock varies depending on the operating voltage range. For detail,

refer to 24.4 AC Characteristics.

Cautions 1. Change the output clock after disabling the PCLBUZ0 pin output (PCLOE0 = 0).

2. To shift to STOP mode, execute the STOP instruction when at least 1.5 cycles of

the clock used for the PCLBUZ0 pin output have elapsed after the PCLBUZ0 pin

output has been disabled.

Remark f

MAIN: Main system clock frequency

Loading...

Loading...