RL78/G10 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 291

Dec 22, 2016

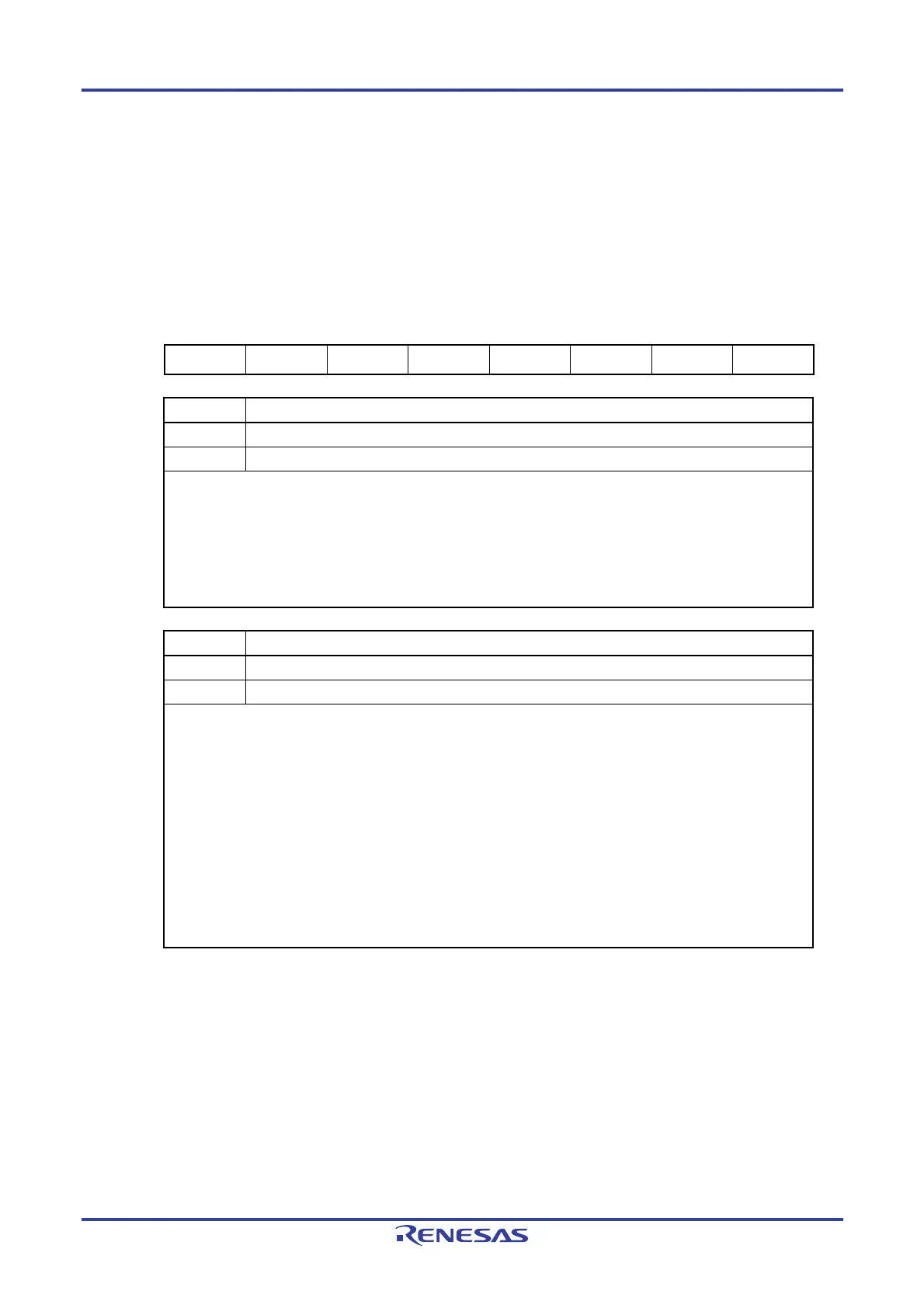

12.3.7 Serial status register 0n (SSR0n)

The SSR0n register indicates the communication status and error occurrence status of channel n. The errors indicated

by this register are framing errors, parity errors, and overrun errors.

The SSR0n register can be read by an 8-bit memory manipulation instruction.

Reset signal generation clears the SSR0n register to 00H.

Figure 12-9. Format of Serial Status Register 0n (SSR0n) (1/2)

Address: F0100H (SSR00) , F0102H (SSR01) , After reset: 00H R

Symbol

7 6 5 4 3 2 1 0

SSR0n 0 TSF0n BFF0n 0 0 FEF0n

Note

PEF0n OVF0n

TSF0n Communication status indication flag of channel n

0 Communication is stopped or suspended.

1 Communication is in progress.

<Clear conditions>

• The ST0n bit of the ST0 register is set to 1 (communication is stopped) or the SS0n bit of the SS0 register is set

to 1 (communication is suspended).

• Communication ends.

<Set condition>

• Communication starts.

BFF0n Buffer register status indication flag of channel n

0 Valid data is not stored in the SDR0nL register.

1 Valid data is stored in the SDR0nL register.

<Clear conditions>

• Transferring transmit data from the SDR0nL register to the shift register ends during transmission.

• Reading receive data from the SDR0nL register ends during reception.

• The ST0n bit of the ST0 register is set to 1 (communication is stopped) or the SS0n bit of the SS0 register is set to

1 (communication is enabled).

<Set conditions>

• Transmit data is written to the SDR0nL register while the TXE0n bit of the SCR0nH register is set to 1

(transmission or transmission and reception mode in each communication mode).

• Receive data is stored in the SDR0nL register while the RXE0n bit of the SCR0nH register is set to 1 (reception or

transmission and reception mode in each communication mode).

• A reception error occurs.

Note Provided in the SSR01 register only.

Caution If data is written to the SDR0nL register when BFF0n = 1, the transmit/receive data stored in

the register is discarded and an overrun error (OVE0n = 1) is detected.

Remark n: Channel number (n = 0, 1)

Loading...

Loading...