RL78/G10 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 284

Dec 22, 2016

12.3.2 Serial clock select register 0 (SPS0)

The SPS0 register is an 8-bit register that is used to select two types of operation clocks (CK00, CK01) that are

commonly supplied to each channel. CK01 is selected by bits 7 to 4 of the SPS0 register, and CK00 is selected by bits 3

to 0.

Rewriting the SPS0 register is prohibited when the operation is enabled (when SE0n = 1).

The SPS0 register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears the SPS0 register to 00H.

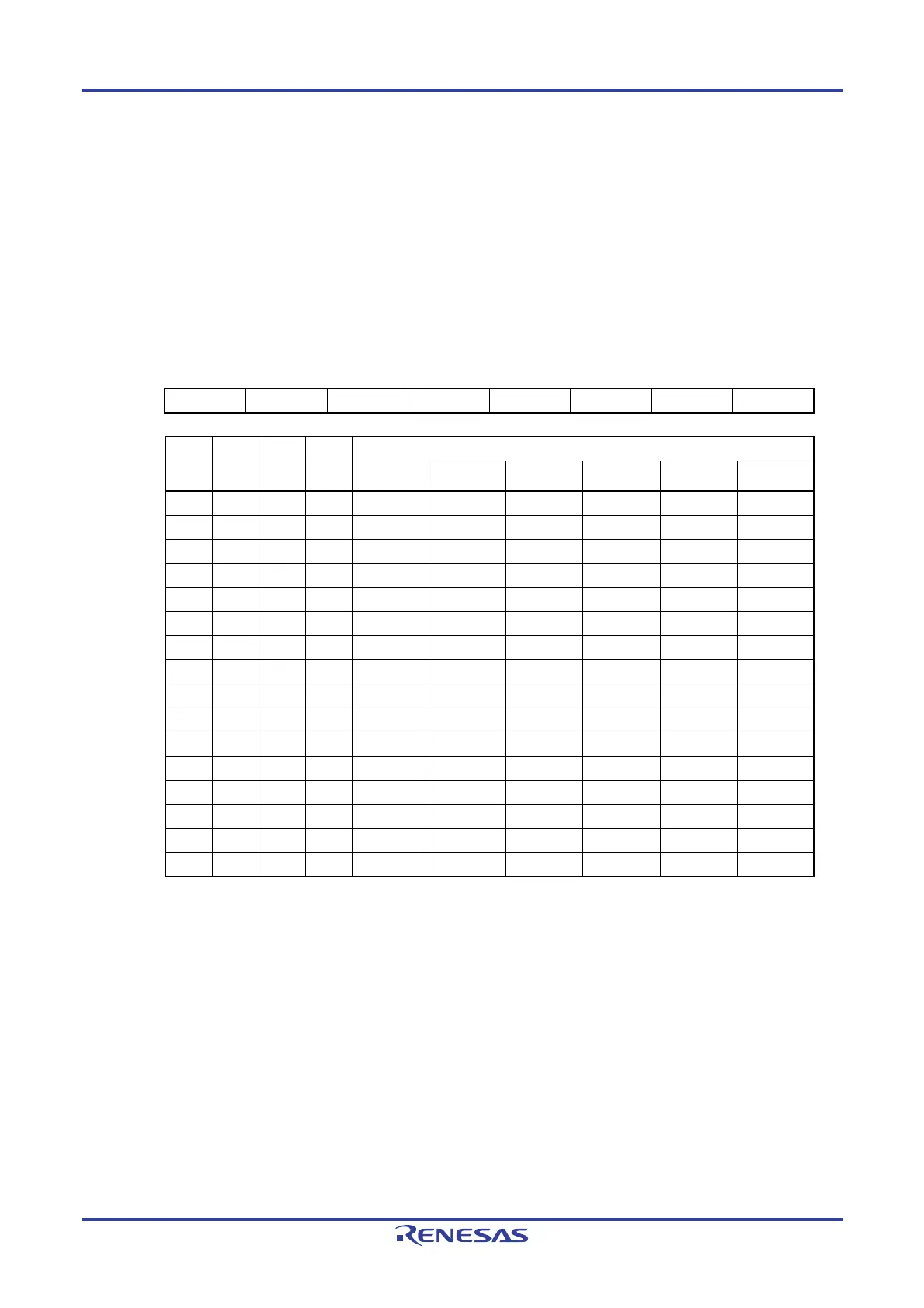

Figure 12-4. Format of Serial Clock Select Register 0 (SPS0)

Address: F0126H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

SPS0 PRS013 PRS012 PRS011 PRS010 PRS003 PRS002 PRS001 PRS000

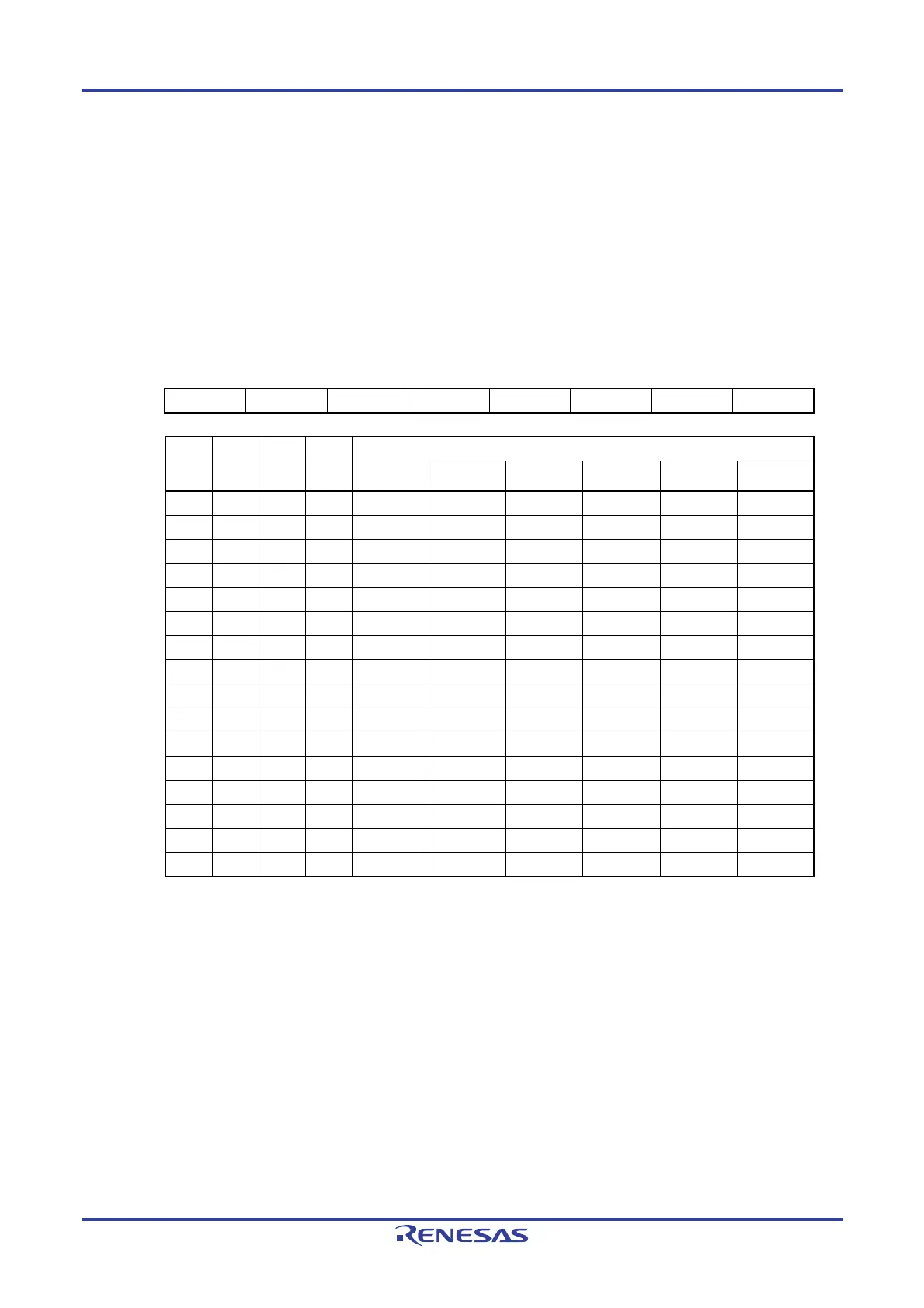

PRS

0n3

PRS

0n2

PRS

0n1

PRS

0n0

Section of operation clock (CKn)

Note

f

CLK =

1.25 MHz

fCLK =

2.5 MHz

fCLK =

5 MHz

fCLK =

10 MHz

fCLK =

20 MHz

0 0 0 0 fCLK 1.25 MHz 2.5 MHz 5 MHz 10 MHz 20 MHz

0 0 0 1 fCLK/2 625 kHz 1.25 MHz 2.5 MHz 5 MHz 10 MHz

0 0 1 0 fCLK/2

2

313 kHz 625 kHz 1.25 MHz 2.5 MHz 5 MHz

0 0 1 1 fCLK/2

3

156 kHz 313 kHz 625 kHz 1.25 MHz 2.5 MHz

0 1 0 0 fCLK/2

4

78 kHz 156 kHz 313 kHz 625 kHz 1.25 MHz

0 1 0 1 fCLK/2

5

39 kHz 78 kHz 156 kHz 313 kHz 625 kHz

0 1 1 0 fCLK/2

6

19.5 kHz 39 kHz 78 kHz 156 kHz 313 kHz

0 1 1 1 fCLK/2

7

9.8 kHz 19.5 kHz 39 kHz 78 kHz 156 kHz

1 0 0 0 fCLK/2

8

4.9 kHz 9.8 kHz 19.5 kHz 39 kHz 78 kHz

1 0 0 1 fCLK/2

9

2.5 kHz 4.9 kHz 9.8 kHz 19.5 kHz 39 kHz

1 0 1 0 fCLK/2

10

1.22 kHz 2.5 kHz 4.9 kHz 9.8 kHz 19.5 kHz

1 0 1 1 fCLK/2

11

625 Hz 1.22 kHz 2.5 kHz 4.9 kHz 9.8 kHz

1 1 0 0 fCLK/2

12

313 Hz 625 Hz 1.22 kHz 2.5 kHz 4.9 kHz

1 1 0 1 fCLK/2

13

152 Hz 313 Hz 625 Hz 1.22 kHz 2.5 kHz

1 1 1 0 fCLK/2

14

78 Hz 152 Hz 313 Hz 625 Hz 1.22 kHz

1 1 1 1 fCLK/2

15

39 Hz 78 Hz 152 Hz 313 Hz 625 Hz

Note When changing the clock selected for f

CLK (by changing the system clock control register (CKC) value),

do so after having stopped (serial channel stop register 0 (ST0) = 03H) the operation of the serial

array unit (SAU).

Remarks 1. fCLK: CPU/peripheral hardware clock frequency

2. n: Channel number (n = 0, 1)

Loading...

Loading...