RL78/G10 CHAPTER 10 A/D CONVERTER

R01UH0384EJ0311 Rev. 3.11 245

Dec 22, 2016

10.3.2 A/D converter mode register 0 (ADM0)

This register sets the conversion time for analog input to be A/D converted, and starts/stops conversion.

The ADM0 register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

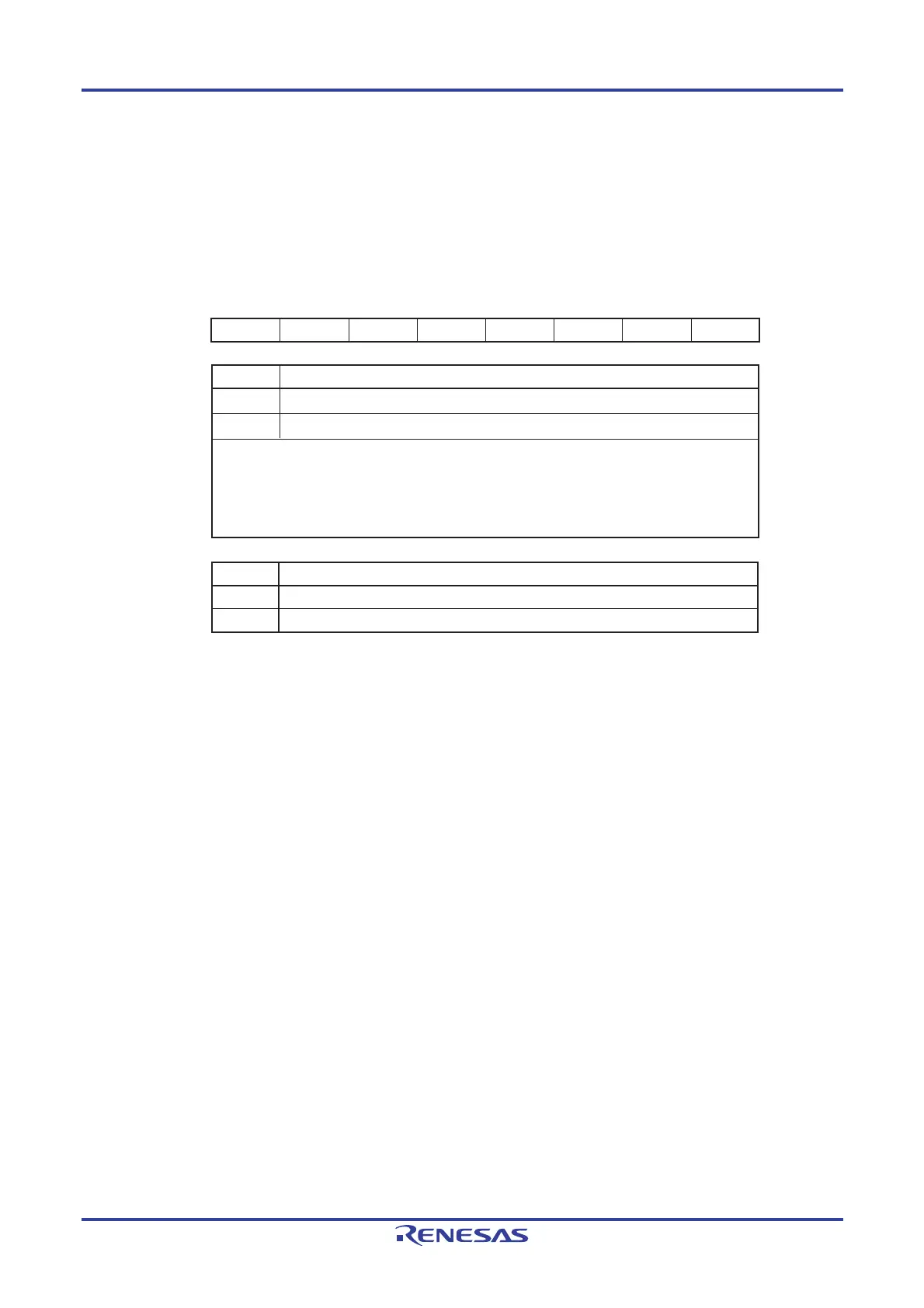

Figure 10-3. Format of A/D Converter Mode Register 0 (ADM0)

ADCELV0

Note 1

FR0

Note 1

FR1

Note 1

00 0ADCS

A/D conversion operation control

Stops conversion operation (conversion stopped/standby status)

ADCS

0

<0>123456<7>

ADM0

Address: FFF30H After reset: 00H R/W

Symbol

A/D voltage comparator operation control

Note 2

Stops A/D voltage comparator operation

Enables A/D voltage comparator operation

ADCE

0

1

Enables conversion operation (conversion operation status)

<Clear conditions>

• 0 is written to ADCS.

• The bit is automatically cleared to 0 when A/D conversion ends.

<Set condition>

• 1 is written to ADCS when the ADCE bit is 1.

1

Notes 1. For details of the FR1, FR0, and LV0 bits and A/D conversion, see Table 10-2 10-Bit

Resolution A/D Conversion Time Selection or Table 10-3 8-Bit Resolution A/D

Conversion Time Selection.

2. The operation of the A/D voltage comparator is controlled by the ADCS and ADCE bits,

and it takes 0.1

μ

s from the start of operation for the operation to stabilize. Therefore,

when the ADCS bit is set to 1 after 0.1

μ

s or more has elapsed from the time ADCE bit is

set to 1, the conversion result at that time has priority over the first conversion result. If

the ADCS bit is set to 1 to perform A/D conversion without waiting for at least 0.1 μs,

ignore data of the conversion.

Cautions 1. Rewrite the values of the FR1, FR0, and LV0 bits in the conversion standby status

(ADCS = 0, ADCE = 1) or in the conversion stopped status (ADCS = 0, ADCE = 0).

Rewriting the values of the FR1, FR0, and LV0 bits, and ADCS bits by an 8-bit

manipulation instruction at the same time is prohibited.

2. Setting ADCS =1 and ADCE = 0 is prohibited. When 1 is written to the ADCS bit in

the conversion stopped status (ADCE = 0, ADCS = 0), the ADCS bit is not set to 1.

3. Changing the ADCE and ADCS bits from 0 to 1 at the same time by using an 8-bit

manipulation instruction is prohibited. Be sure to set these bits in the order

described in 10.7 A/D Converter Setup Flowchart.

4. Be sure to clear bits 2, 5, and 6 to 0.

5. Setting the ADCS bit to 1 during conversion (ADCS = 1) is prohibited. When

restarting the conversion for the same channel is required, stop conversion once

(ADCS = 0), and then restart the A/D conversion (ADCS = 1).

Loading...

Loading...