RL78/G10 CHAPTER 6 TIMER ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 150

Dec 22, 2016

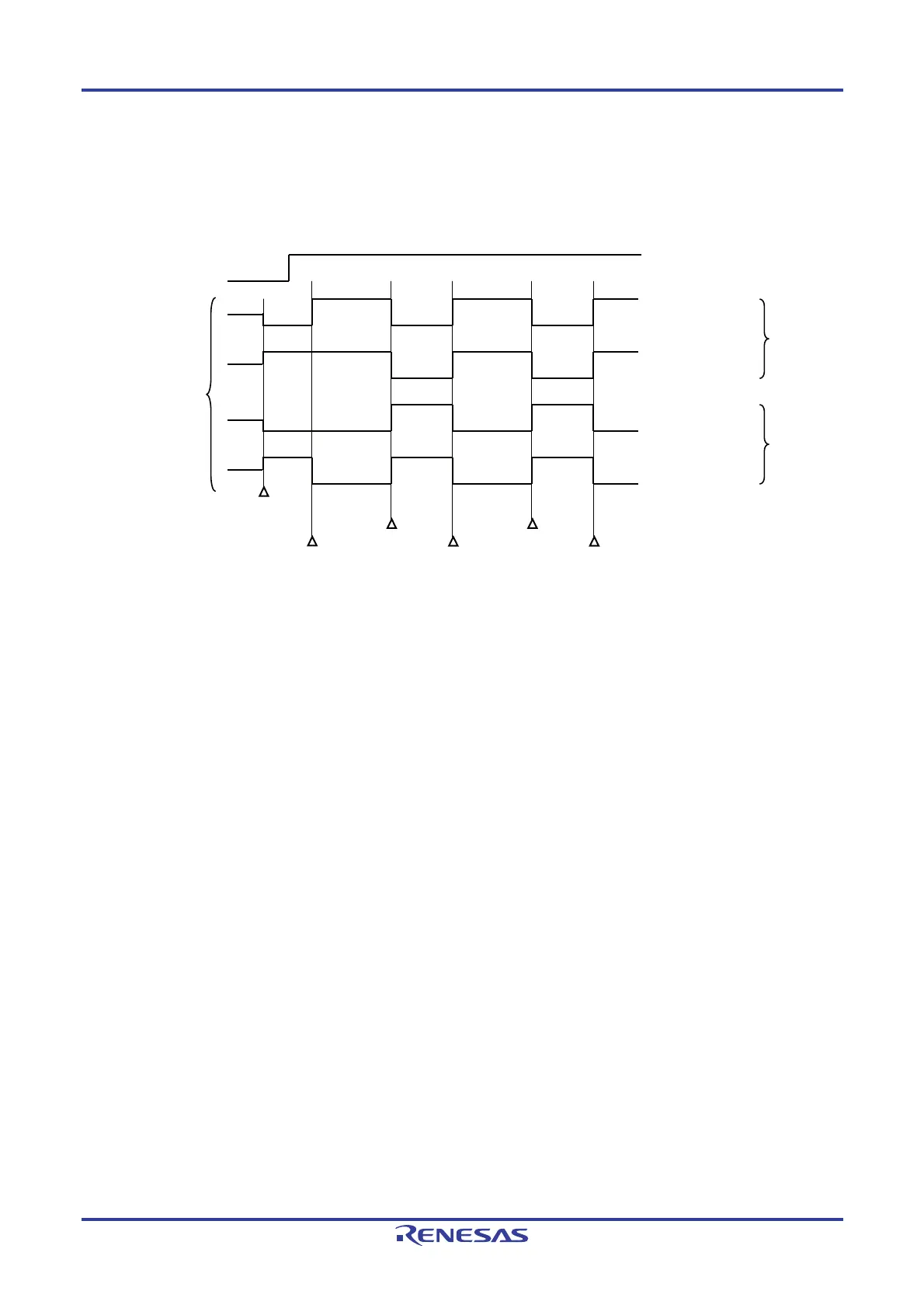

(b) When operation starts with slave channel output mode (TOM0p = 1) setting (PWM output)

When slave channel output mode (TOM0p = 1), the active level is determined by timer output level register 0

(TOL0p) setting.

Figure 6-32. TO0p Pin Output Status at PWM Output (TOM0p = 1)

Hi-Z

Active

TOE0p

Default

status

Set

Reset

Set

Reset

Set

Port output is enabled

TO0p

(output)

ActiveActive

TO0p bit = 0

(Default status : Low)

TO0p bit = 1

(Default status : High)

TO0p bit = 0

(Default status : Low)

TO0p bit = 1

(Default status : High)

TOL0p bit = 0

(Active high)

TOL0p bit = 1

(Active low)

Remarks 1. Set: The output signal of the TO0p pin changes from inactive level to active level.

Reset: The output signal of the TO0p pin changes from active level to inactive level.

2. p: Channel number (n < p ≤ 3)

Loading...

Loading...