RL78/G10 CHAPTER 6 TIMER ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 151

Dec 22, 2016

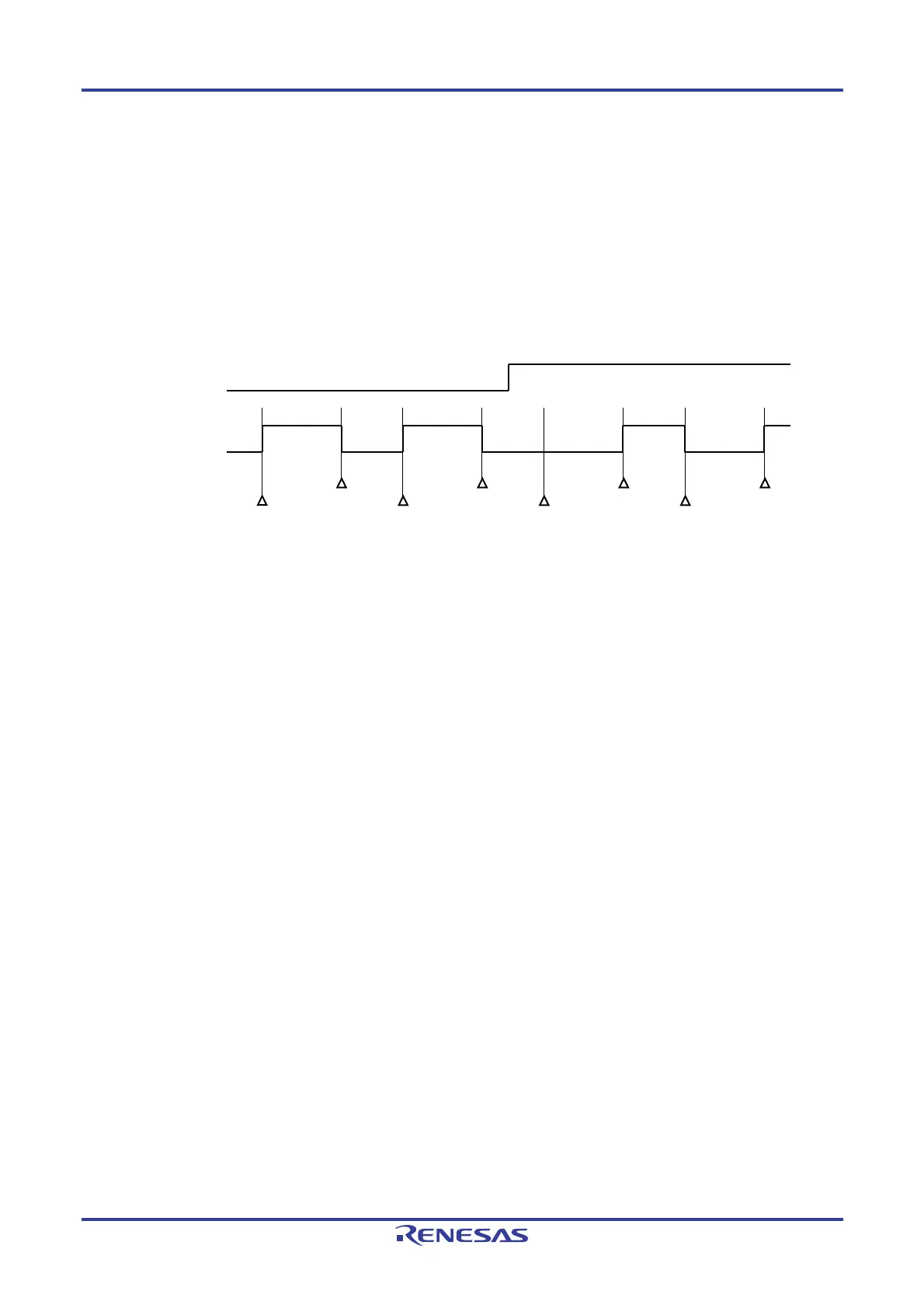

(3) Operation of TO0n pin in slave channel output mode (TOM0n = 1)

(a) When timer output level register 0 (TOL0) setting has been changed during timer operation

When the TOL0 register setting has been changed during timer operation, the setting becomes valid at the

generation timing of the TO0n pin change condition. Rewriting the TOL0 register does not change the output

level of the TO0n pin.

The operation when TOM0n is set to 1 and the value of the TOL0 register is changed while the timer is

operating (TE0n = 1) is shown below.

Figure 6-33. Operation when TOL0 Register Has Been Changed during Timer Operation

TO0n (

Output

)

TOL0

Set

Reset

Set

Reset

Set

Reset

Set

Reset

Active Active Active Active

Remarks 1. Set: The output signal of the TO0n pin changes from inactive level to active level.

Reset: The output signal of the TO0n pin changes from active level to inactive level.

2. n: Channel number

n = 0, 1 (for 10-pin products); n = 0 to 3 (for 16-pin products)

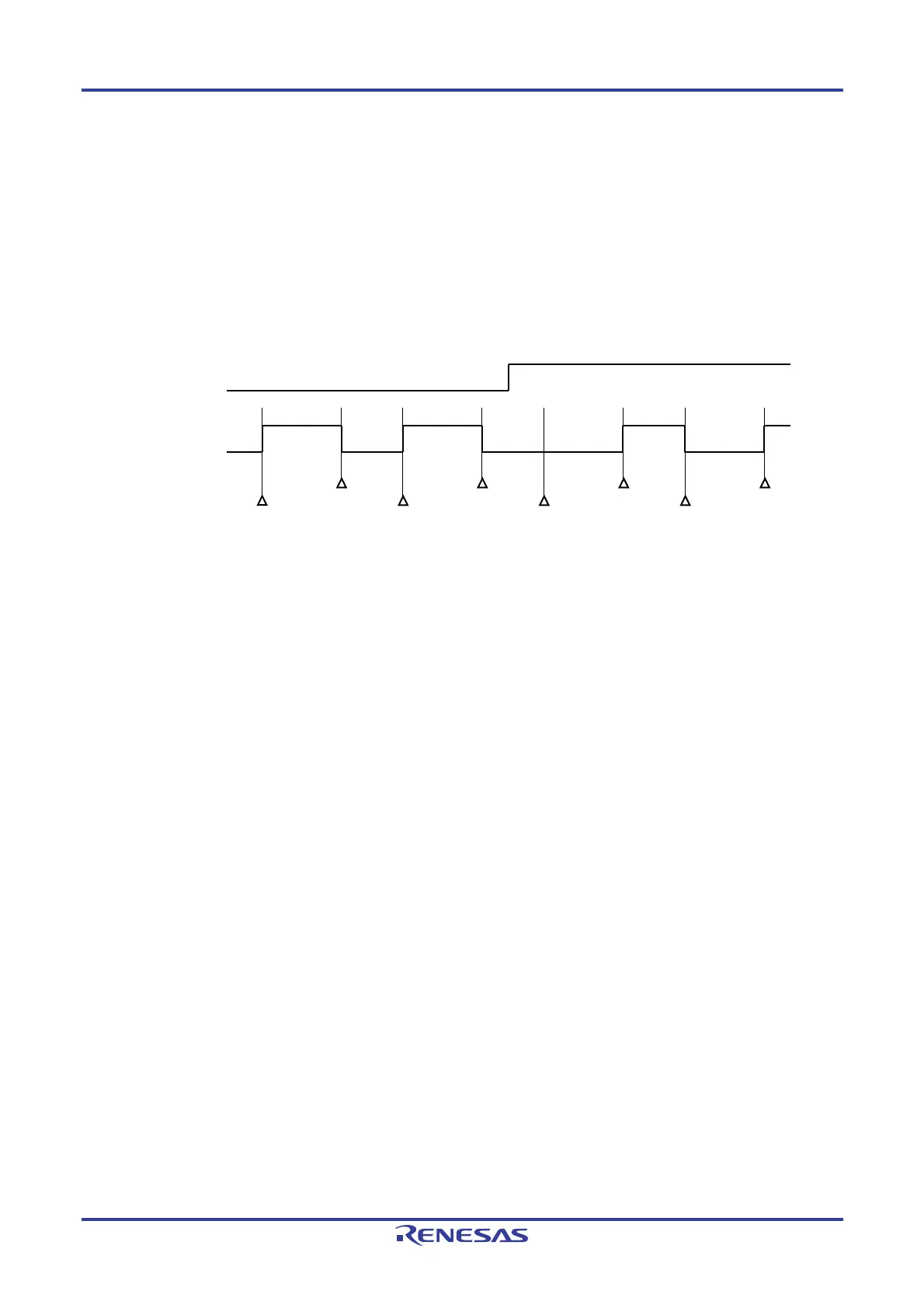

(b) Set/reset timing

To realize 0%/100% output at PWM output, the TO0n pin/TO0n bit set timing at master channel interrupt

request signal (INTTM0n) generation is delayed by one cycle of the count clock (fTCLK) by the slave channel.

If the set condition and reset condition are generated at the same time, a higher priority is given to the latter.

Figure 6-34 shows the set/reset operating statuses where the master/slave channels are set as follows.

Master channel: TOE0n = 1, TOM0n = 0, TOL0n = 0

Slave channel: TOE0p = 1, TOM0p = 1, TOL0p = 0

Loading...

Loading...