RL78/G10 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 343

Dec 22, 2016

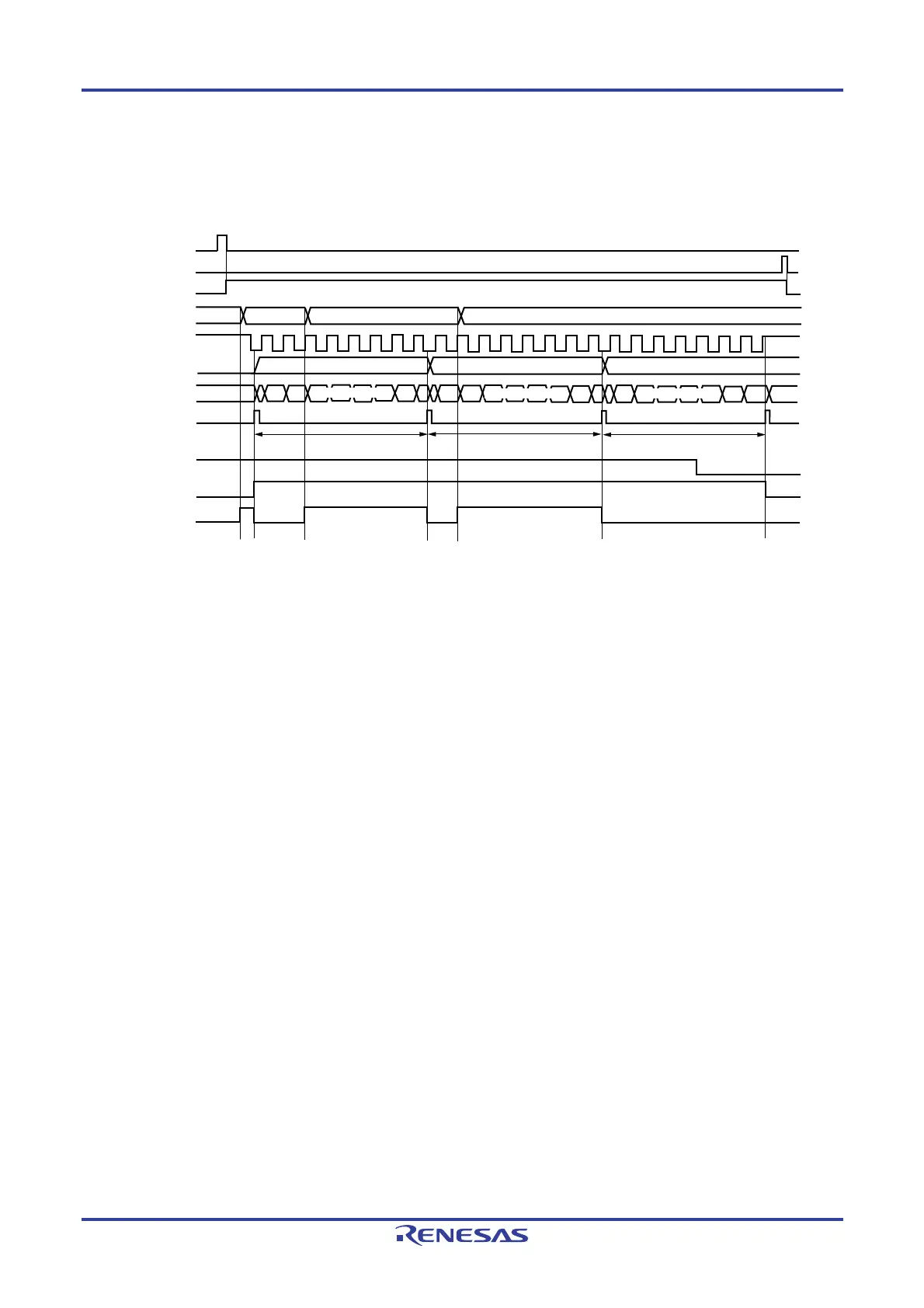

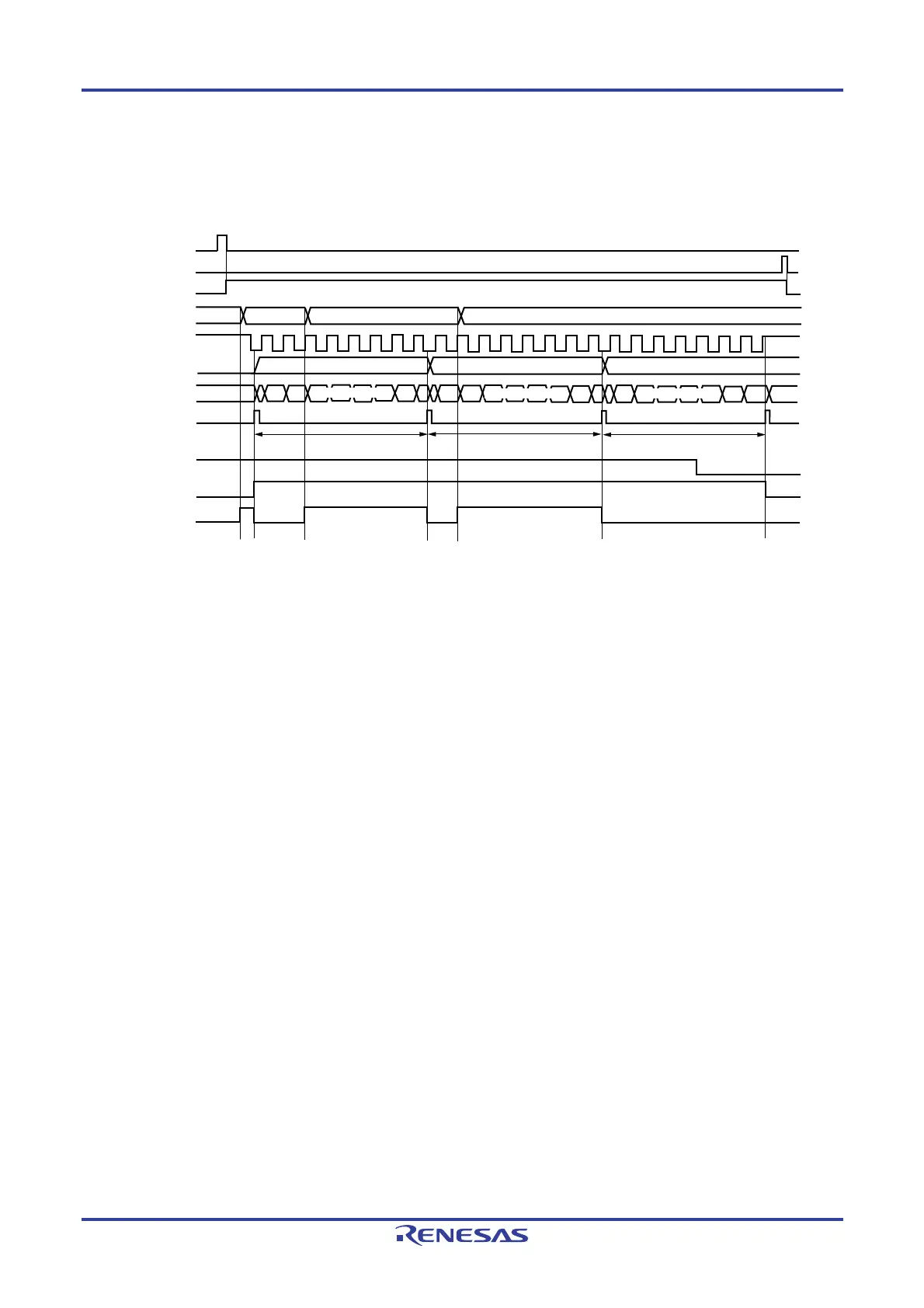

(4) Processing flow (in continuous transmission mode)

Figure 12-52. Timing Chart of Slave Transmission (in Continuous Transmission Mode)

(Type 1: DAP0n = 0, CKP0n = 0)

SS0n

SE0n

SDR0nL

SCKp pin

SOp pin

INTCSIp

TSF0n

BFF0n

MD0n0

ST0n

Shift

register 0n

Transmit data 1

Transmit data 2 Transmit data 3

Transmit data 3Transmit data 2

Transmit data 1

Shift operation

Shift operation Shift operation

Data transmission Data transmission Data transmission

<1>

<6>

<2> <2> <2><3> <3> <3>

<4>

<5>

(Note)

Note If transmit data is written to the SDR0nL register while the BFF0n bit of serial status register 0n (SSR0n) is 1

(valid data is stored in serial data register 0n (SDR0nL)), the transmit data is overwritten.

Caution The MD0n0 bit of serial mode register 0n (SMR0nL) can be rewritten even during operation.

However, rewrite it before transfer of the last bit is started.

Remark n = 0, 1, p: CSI number (p = 00, 01)

Loading...

Loading...