RL78/G10 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 406

Dec 22, 2016

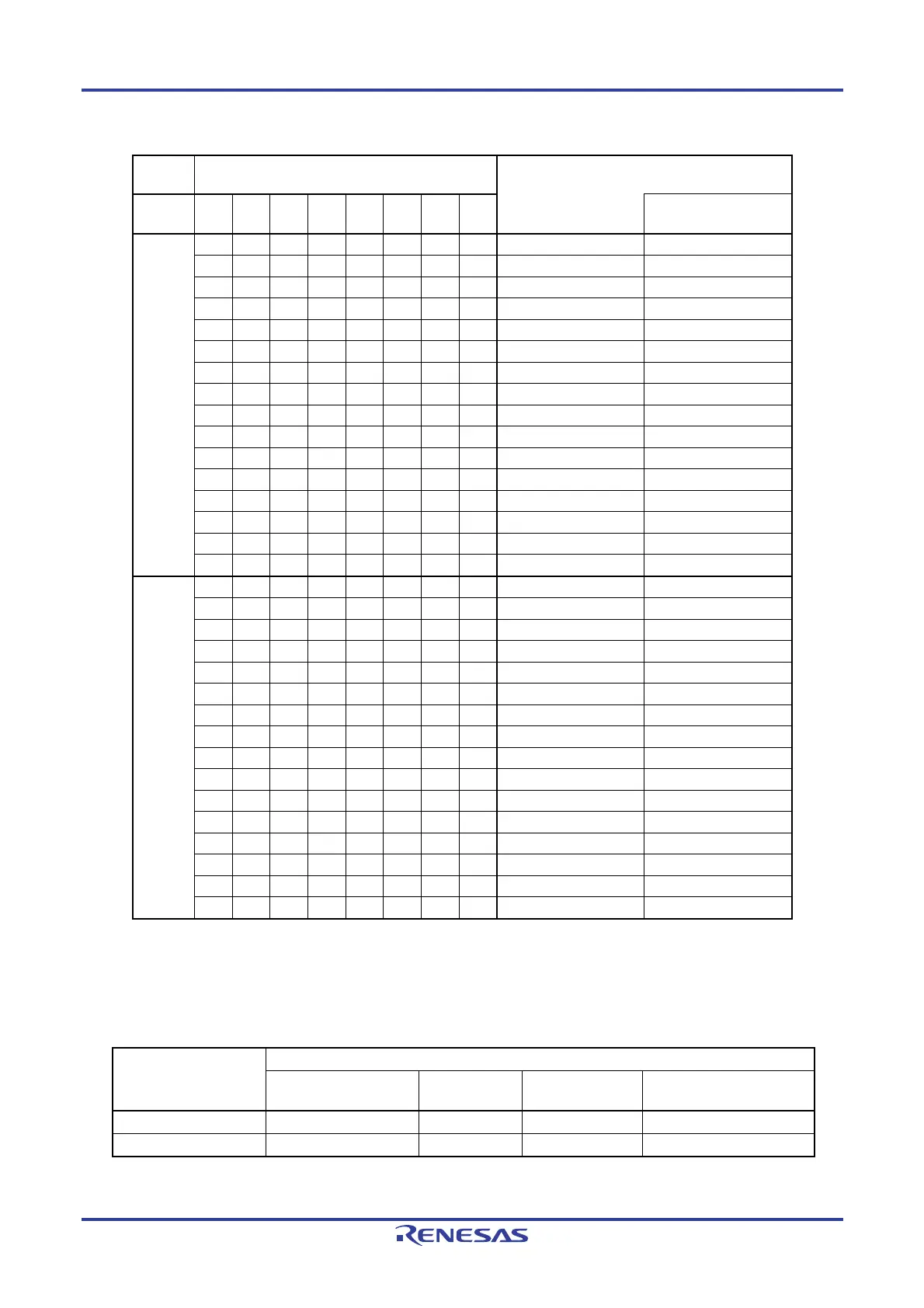

Table 12-4. Selection of Operation Clock for Simplified I

2

C

SMR0n

Register

SPS0 Register Operation Clock (fMCK)

Note

CKS0n PRS

13

PRS

12

PRS

11

PRS

10

PRS

03

PRS

02

PRS

01

PRS

00

fCLK = 20 MHz

0 X X X X 0 0 0 0 fCLK 20 MHz

X X X X 0 0 0 1 fCLK/2 10 MHz

X X X X 0 0 1 0 fCLK/2

2

5 MHz

X X X X 0 0 1 1 fCLK/2

3

2.5 MHz

X X X X 0 1 0 0 fCLK/2

4

1.25 MHz

X X X X 0 1 0 1 fCLK/2

5

625 KHz

X X X X 0 1 1 0 fCLK/2

6

312.5 kHz

X X X X 0 1 1 1 fCLK/2

7

156.2 kHz

X X X X 1 0 0 0 fCLK/2

8

78.1 kHz

X X X X 1 0 0 1 fCLK/2

9

39.1 kHz

X X X X 1 0 1 0 fCLK/2

10

19.5 kHz

X X X X 1 0 1 1 fCLK/2

11

9.77 kHz

X X X X 1 1 0 0 fCLK/2

12

4.87 kHz

X X X X 1 1 0 1 fCLK/2

13

2.44 kHz

X X X X 1 1 1 0 fCLK/2

14

1.22 kHz

X X X X 1 1 1 1 fCLK/2

15

610 Hz

1 0 0 0 0 X X X X fCLK 20 MHz

0 0 0 1 X X X X fCLK/2 10 MHz

0 0 1 0 X X X X fCLK/2

2

5 MHz

0 0 1 1 X X X X fCLK/2

3

2.5 MHz

0 1 0 0 X X X X fCLK/2

4

1.25 MHz

0 1 0 1 X X X X fCLK/2

5

625 KHz

0 1 1 0 X X X X fCLK/2

6

312.5 KHz

0 1 1 1 X X X X fCLK/2

7

156.2 kHz

1 0 0 0 X X X X fCLK/2

8

78.1 kHz

1 0 0 1 X X X X fCLK/2

9

39.1 kHz

1 0 1 0 X X X X fCLK/2

10

19.5 kHz

1 0 1 1 X X X X fCLK/2

11

9.76 kHz

1 1 0 0 X X X X fCLK/2

12

4.87 kHz

1 1 0 1 X X X X fCLK/2

13

2.44 kHz

1 1 1 0 X X X X fCLK/2

14

1.22 kHz

1 1 1 1 X X X X fCLK/2

15

610 Hz

Note When changing the clock selected for fCLK (by changing the system clock control register (CKC) value), do so

after having stopped (serial channel stop register 0 (ST0) = 000FH) the operation of the serial array unit (SAU).

Remarks 1. X: don’t care

2. n = 0

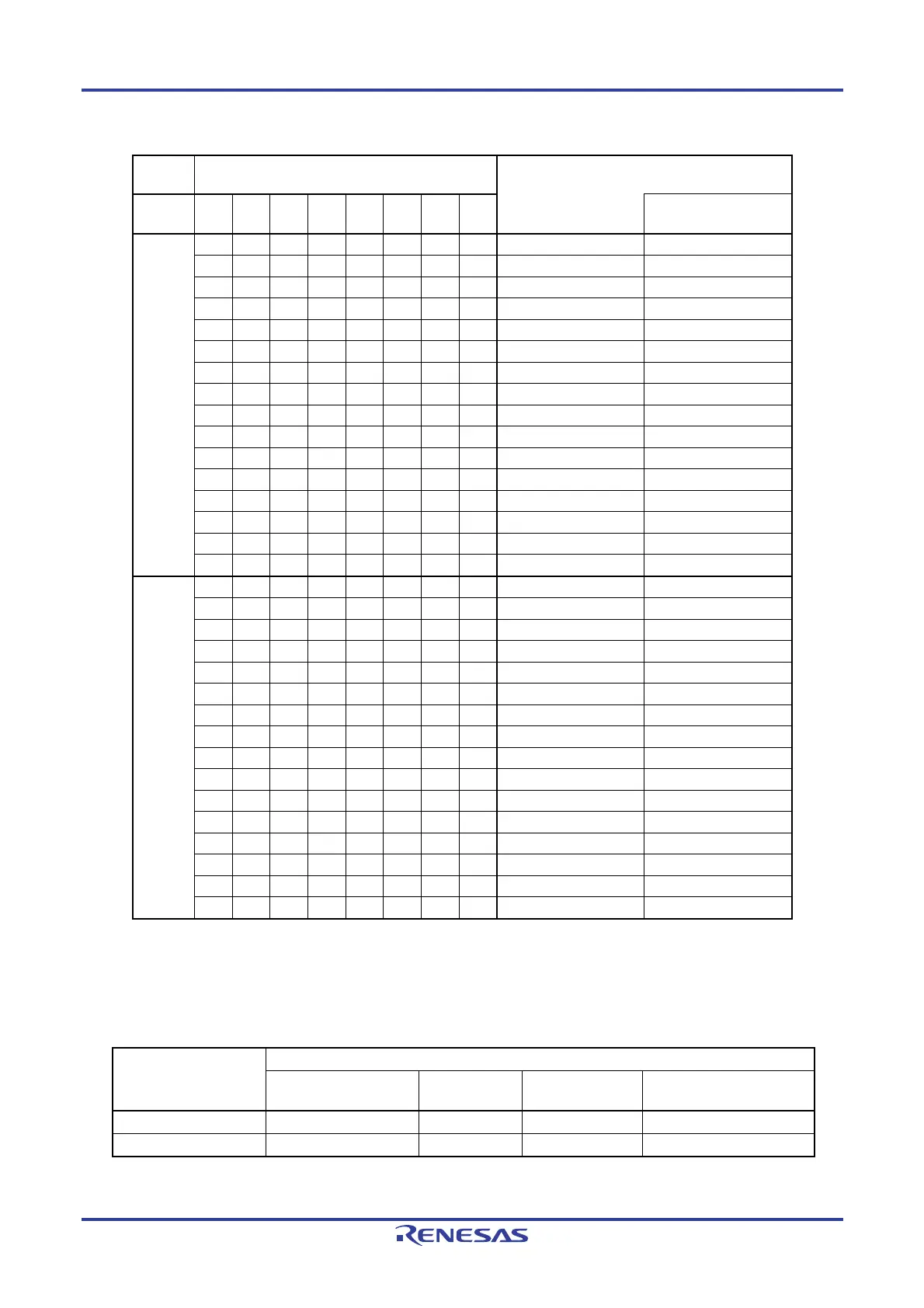

Here is an example of setting an IIC transfer rate where f

MCK = fCLK = 20 MHz.

IIC Transfer Mode

(Desired Transfer Rate)

fCLK = 20 MHz

Operation Clock (fMCK) SDR0nH[7:1] Calculated

Transfer Rate

Error from Desired Transfer

Rate

100 kHz fCLK/2 49 100 kHz 0.0%

400 kHz fCLK 25 384.6 kHz 3.8%

Note

Note The error cannot be set to about 0% because the duty ratio of the SCL signal is 50%.

Loading...

Loading...