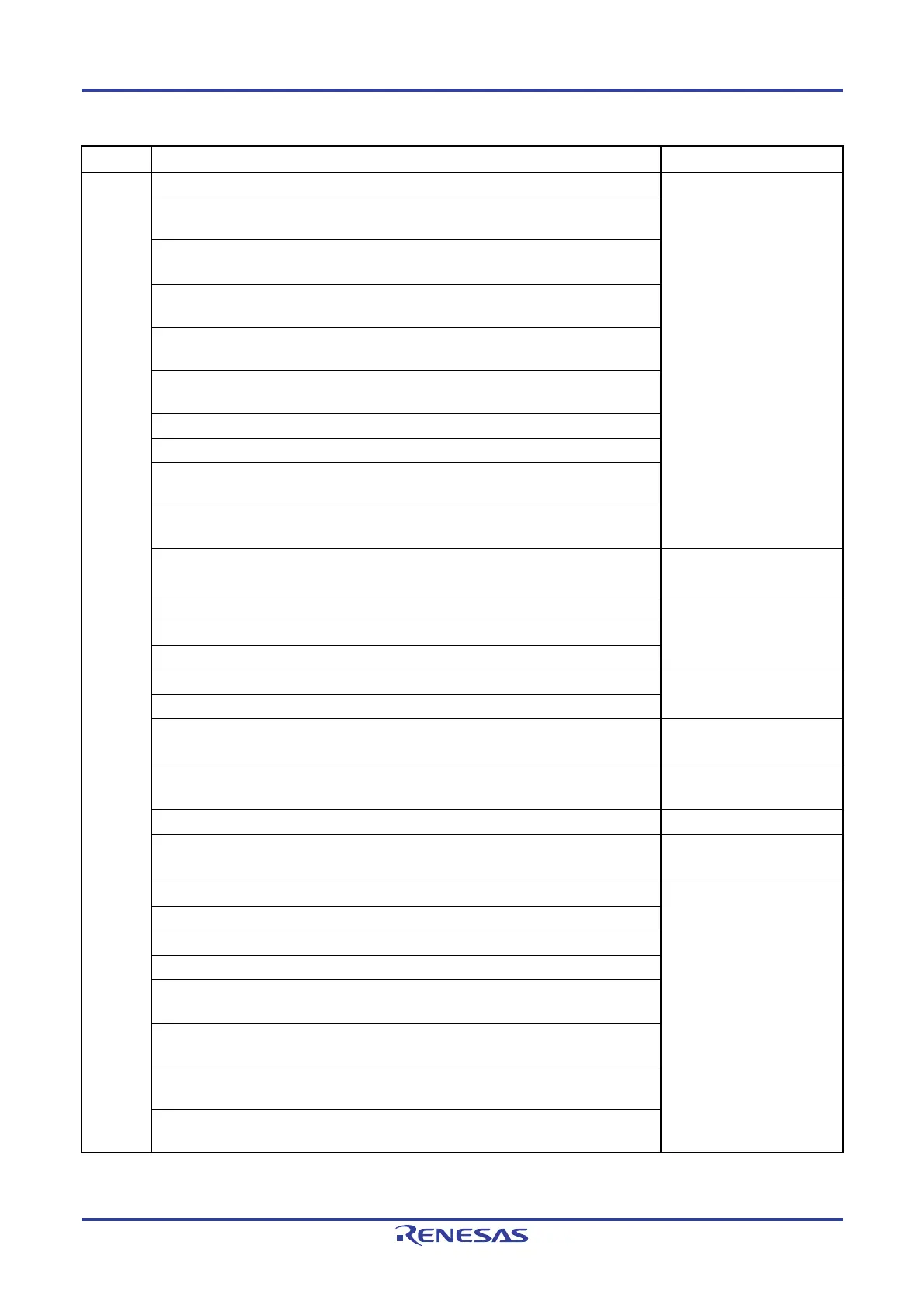

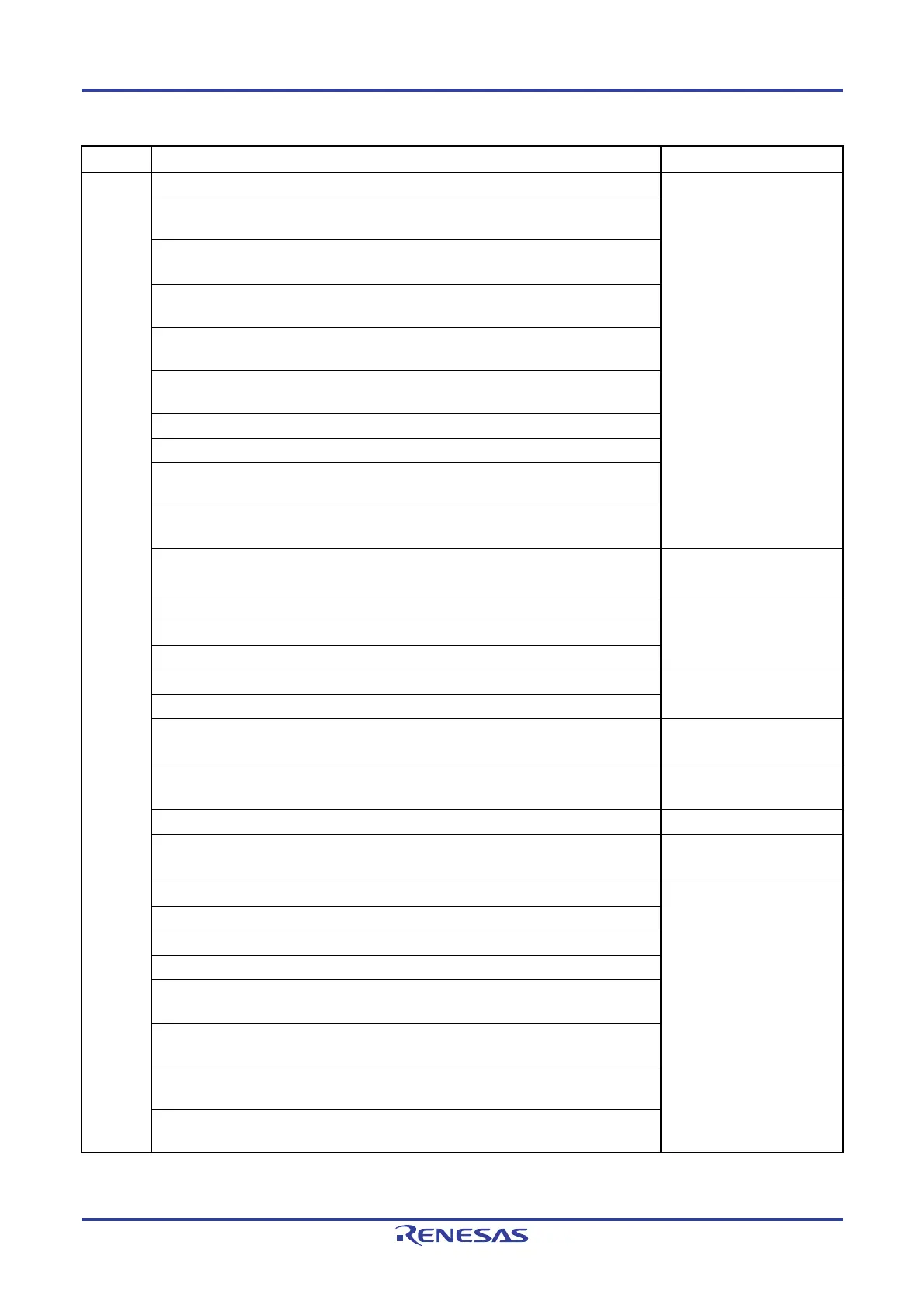

RL78/G10 APPENDIX A REVISION HISTORY

R01UH0384EJ0311 Rev. 3.11 616

Dec 22, 2016

(8/9)

Edition

Description Chapter

Rev.1.00

Modification of error in Figure 6-16 Format of Timer Output Enable Register 0 (TOE0)

CHAPTER 6

TIMER ARRAY UNIT

Addition of caution in 6.4.2 Basic rules of 8-bit timer operation function (only channels 1

and 3)

Modification of error in Figure 6-26 Operation Timing (In Capture Mode: Input Pulse

Interval Measurement)

Modification of error in Figure 6-28 Operation Timing (In Capture & One-count Mode:

High-level Width Measurement)

Addition of caution in Figure 6-41 Operation Procedure of Interval Timer/Square Wave

Output Function

Modification of error in Figure 6-61 Operation Procedure When Delay Counter Function Is

Used

Addition of caution in 6.8.2 Operation as PWM function

Addition of caution in 6.8.3 Operation as multiple PWM output function

Modification of Figure 6-74 Example of Set Contents of Registers When Multiple PWM

Output Function (Master Channel) Is Used

Modification of Figure 6-75 Example of Set Contents of Registers When Multiple PWM

Output Function (Slave Channel) Is Used (Output Two Types of PWMs)

Modification of error in Figure 7-2 Format of Peripheral Enable Register 0 (PER0)

CHAPTER 7

12-BIT INTERVAL TIMER

Modification of cautions in Figure 8-2 Format of Clock Output Select Register 0 (CKS0)

CHAPTER 8

CLOCK OUTPUT/BUZZER

OUTPUT CONTROLLER

Addition of note in Figure 8-3 Format of Port Mode Registers 0, 4 (PM0, PM4)

Modification of description in 8.4.1 Operation as output pin

Modification of Figure 10-13 Conversion Operation of A/D Converter CHAPTER 10

A/D CONVERTER

Modification of Table 10-5 Resistance and Capacitance Values of Equivalent Circuit

Modification of description in Figure 12-21 Peripheral Enable Register 0 (PER0) Setting

When Stopping Operation by Units

CHAPTER 12

SERIAL ARRAY UNIT

Addition of note in Figure 12-22 Each Register Setting When Stopping Operation by

Channels

Modification of error in 12.7 Operation of Simplified I

2

C (IIC00) Communication

Modification of caution in Figure 14-5 Format of External Interrupt Rising Edge Enable

Register (EGP0) and External Interrupt Falling Edge Enable Register (EGN0)

CHAPTER 14 INTERRUPT

FUNCTIONS

Modification of error in Table 15-1 Assignment of Key Interrupt Detection Pins

CHAPTER 15

KEY INTERRUPT FUNCTION

Modification of caution in Figure 15-3 Format of Key Return Mode Register (KRM0)

Addition of caution in Figure 15-4 Format of Key Return Flag Register (KRF)

Addition of note in Figure 15-5 Format of Port Mode Registers 0, 4 (PM0, PM4)

Modification of note in Figure 15-6 Operation of INTKR Signal When a Key Interrupt is

Input to a Single Channel (When KRMD = 0 and KREG = 0)

Modification of note in Figure 15-7 Operation of INTKR Signal When Key Interrupts Are

Input to Multiple Channels (When KRMD = 0 and KREG = 0)

Modification of note in Figure 15-8 Basic Operation of the INTKR Signal When the Key

Interrupt Flag Is Used (When KRMD = 1 and KREG = 0)

Modification of Figure 15-9 Operation of INTKR Signal When Key Interrupts Are Input to

Multiple Channels (When KRMD = 1 and KREG = 0)

Loading...

Loading...