RL78/G10 CHAPTER 5 CLOCK GENERATOR

R01UH0384EJ0311 Rev. 3.11 77

Dec 22, 2016

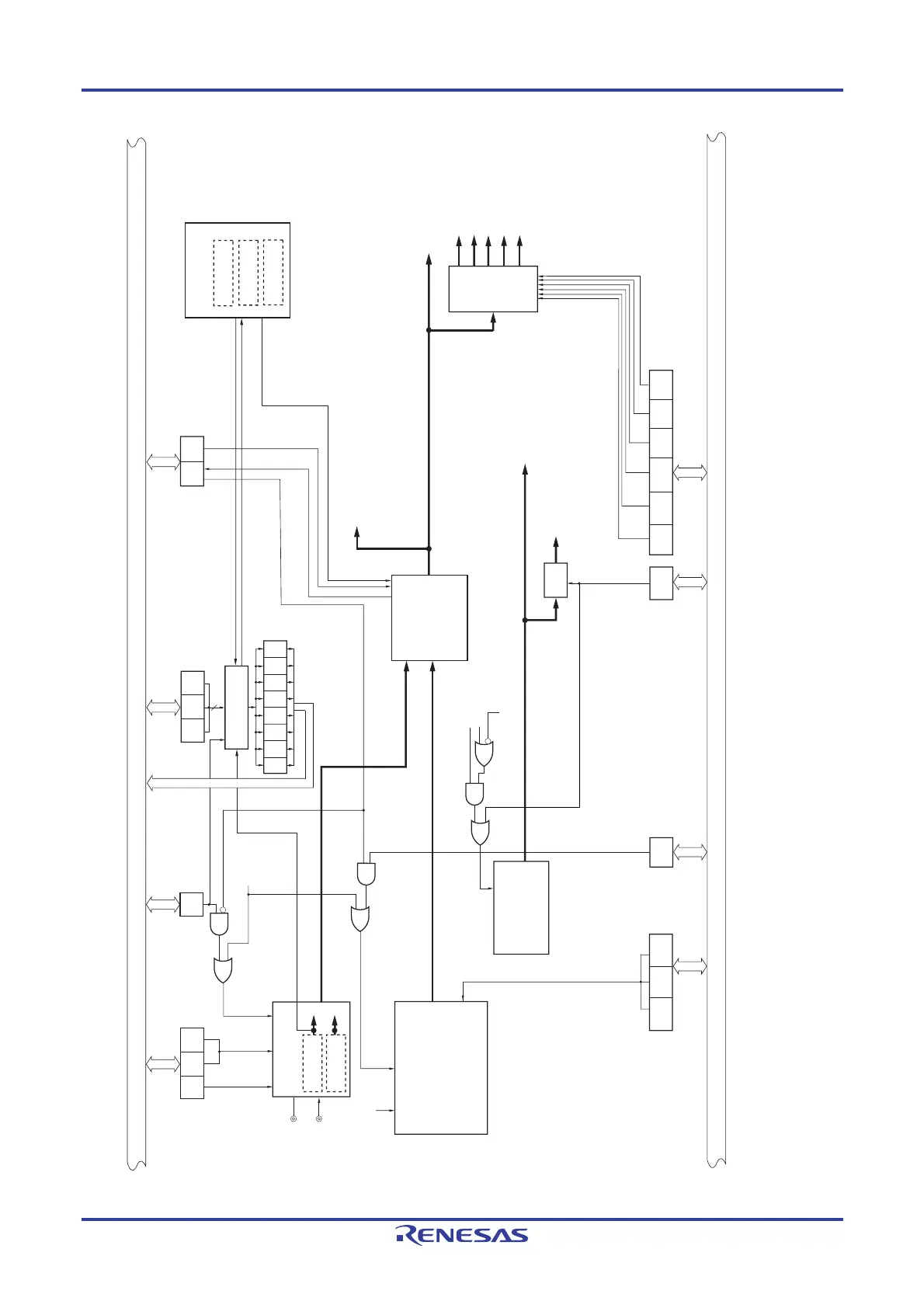

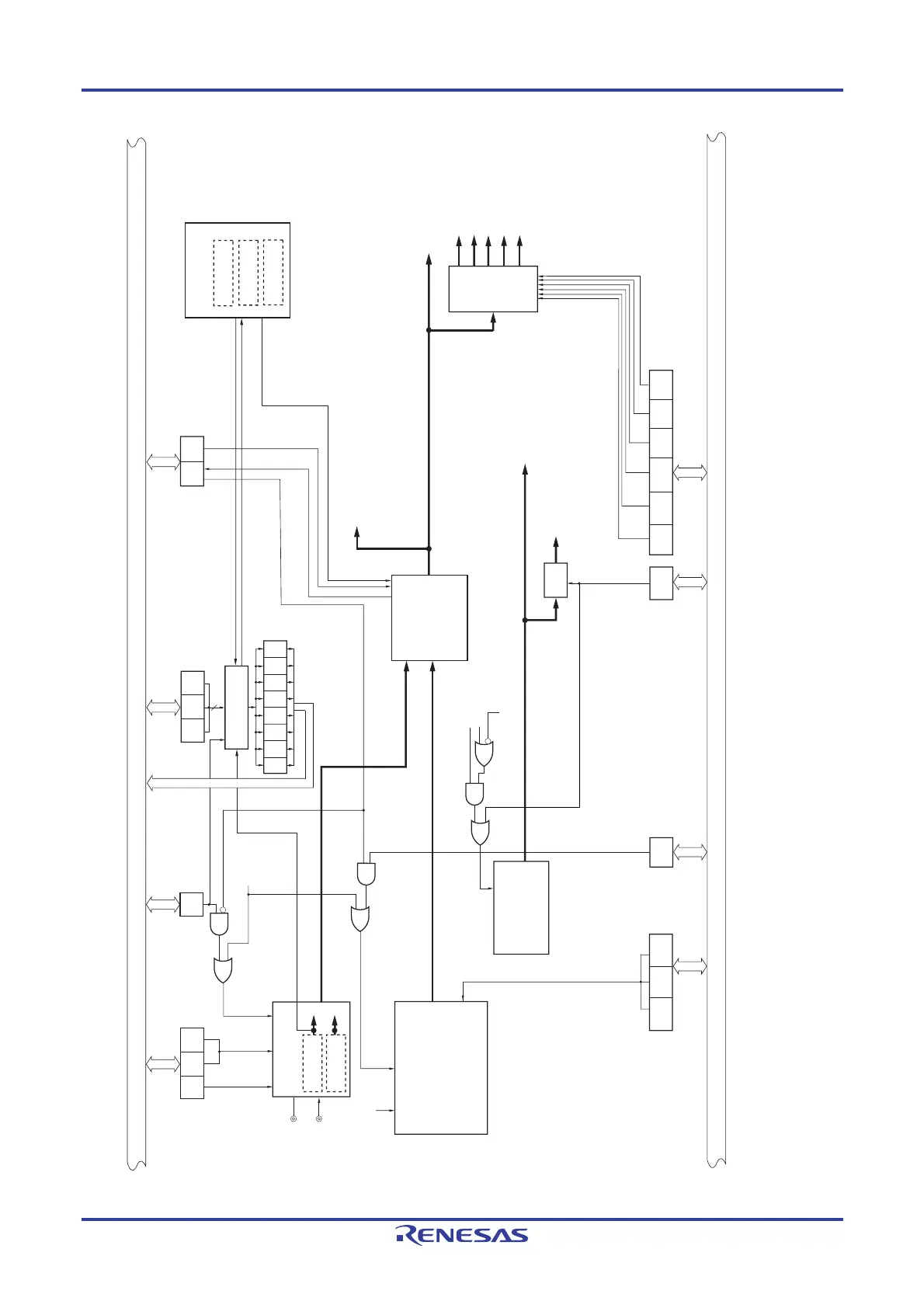

Figure 5-1. Block Diagram of Clock Generator

SAU0

EN

3

Clock operation mode

control register

(CMC)

Note

Clock operation status

control register

(CSC)

Note

MSTOP

EXCLK

OSCSEL

AMPH

STOP mode

signal

f

MX

X1/P121/

(INTP3)

Note

X2/EXCLK/P122/

(INTP2)

Note

f

X

f

EX

Crystal/ceramic

oscillation

External

input clock

High-speed system

clock oscillator

Note

High-speed on-chip oscillator

Option byte (000C2H)

FRQSEL0 to FRQSEL2

f

IH

Low-speed on-chip

oscillator

Option byte (000C0H)

WDTON

WDSTBYON

HALT/STOP mode signal

HIOSTOP

Internal bus

Clock operation status

control register

(CSC)

Note

High-speed on-chip oscillator

frequency selection register

(HOCODIV)

TAU 0

EN

IICA0

EN

Note

ADC

EN

Peripheral enable

register 0 (PER0)

f

CLK

CPU

Watchdog timer

Timer array unit

Serial array unit

A/D converter

Comparator

Note

Serial interface IICA

Note

Controller

Clock output/buzzer output

Main system clock

source selector

System clock control

register (CKC)

Note

MCM0

MCS

Normal

operation mode

HALT m od e

STOP mode

Standby controller

Oscillation stabilization

time select register (OSTS)

Note

Oscillation stabilization

time counter status

register (OSTC)

Note

Internal bus

OSTS1 OSTS0OSTS2

MOST

9

MOST

8

MOST

11

MOST

10

MOST

15

MOST

13

MOST

18

MOST

17

X1 oscillation

stabilization time counter

20/10/5/2.5/1.25 MHz (typ.)

HOCODIV2 HOCODIV1 HOCODIV0

15 kHz (typ.)

f

IL

WUTMMCK0

Operation speed

mode control register

(OSMC)

Note

Controller

12 bits Interval timer

Note

TMKA

EN

Note

CMP

EN

Note

Note 16-pin products only.

Loading...

Loading...