RL78/G10 CHAPTER 6 TIMER ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 111

Dec 22, 2016

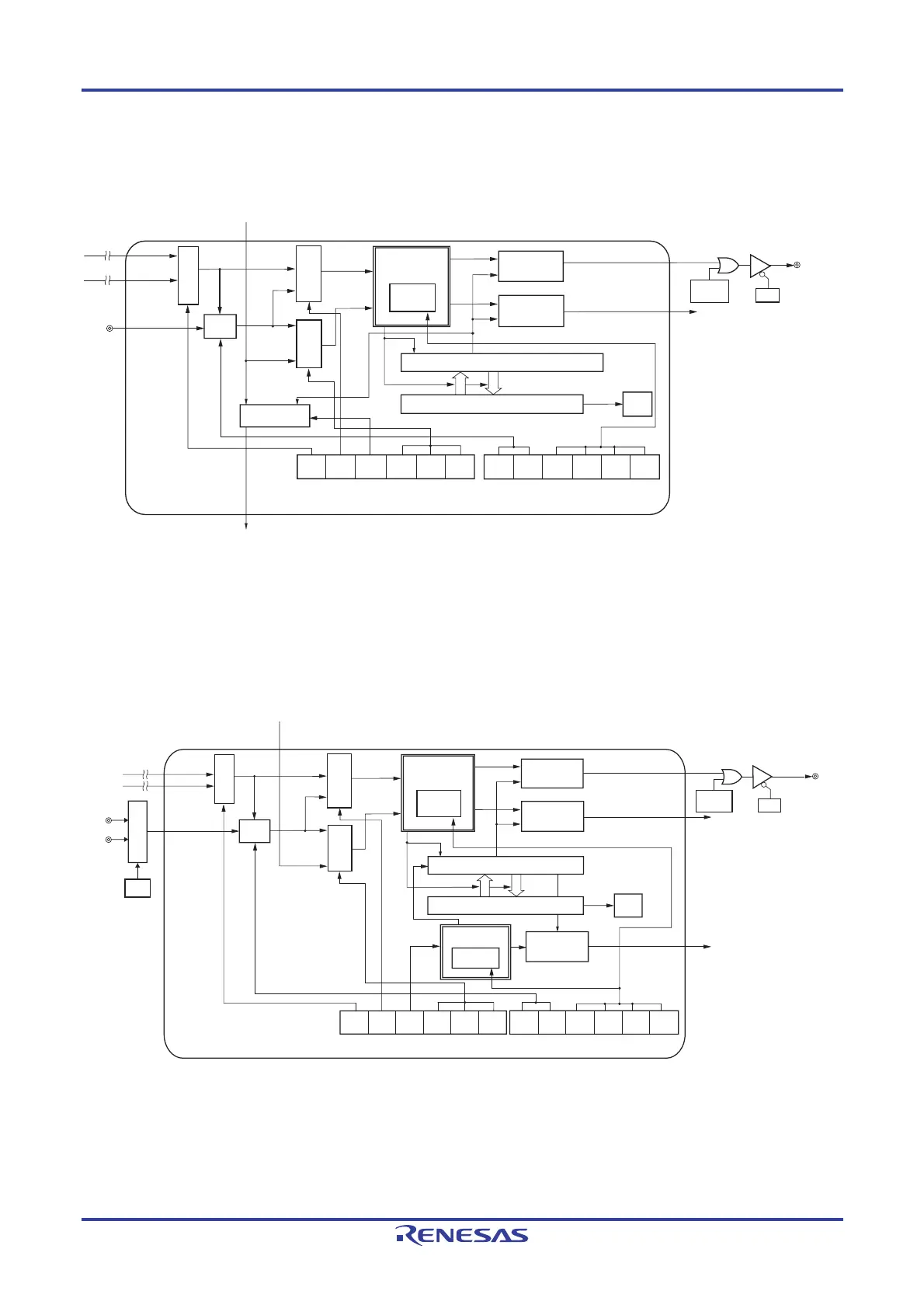

Figure 6-2. Internal Block Diagram of Channel of Timer Array Unit

(a) Channels 0 and 2

(Timer interrupt)

Timer status

register 0n (TSR0n)

Overflow

Timer mode register 0n (TMR0nH, TMR0nL)

TMR0nL

Note 2

Note 2

Interrupt signal from master channel

Note 1

Interrupt signal to slave channel

TO00

T

O02

PMxx

CKS0n1

CCS0n STS0n2

STS0n

1

STS0n0

MD0n2CIS0n1CIS0n0

MD0n3

MD0n1

MD0n0

OVF

0n

INTTM0n

CK00

CK01

TI00

TI02

f

MCK

f

TCLK

TMR0nLTMR0nH

MAS

TER02

Interrupt

controller

Output

controller

Timer controller

Mode

selection

Trigger

selection

Count clock

selection

Slave/master

controller

Edge

detection

Operating

clock selection

Timer data register 0n (TDR0nH, TDR0nL)

Timer counter register 0n (TCR0nH, TCR0nL)

Note 1

Output latch

(Pxx)

Notes 1. Channel 2 only.

2. 16-pin products only.

Remark n = 0, 2

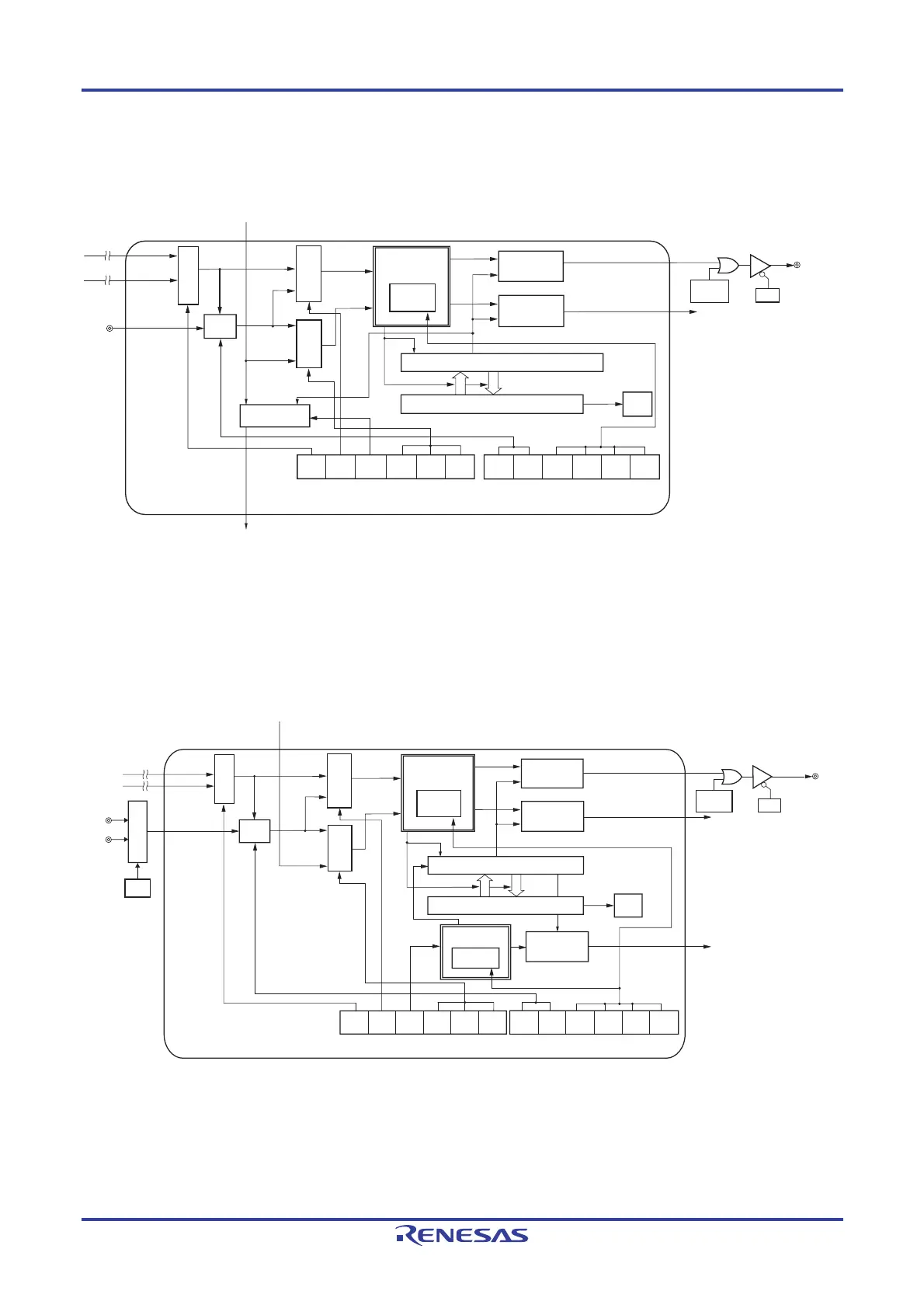

(b) Channel 1

TO01

PMxx

OVF

0n

INTTM0n

(T

imer interrupt)

CK00

CK01

f

MCK

fTCLK

INTTM0nH

(T

imer interrupt)

Interrupt

controller

Output

controller

Output latch

(Pxx)

Timer status

register 01 (TSR01)

Overflow

Timer data register 01 (TDR01)

Timer counter register 01 (TCR01)

Timer mode register 0n (TMR0nH, TMR0nL)

TMR0nH

TMR0nL

Timer controller

Trigger

selection

Count clock

selection

Mode

selection

Edge

detection

Operating

clock selection

Interrupt signal from master channel

8-bit timer

controller

Mode

selection

Interrupt

controller

TI01

RxD0

ISC

Input switch control

register (ISC)

Selector

CKS0n1

CCS0n

SPLIT

0n

STS0n

2STS0n1 STS0n0 MD0n2CIS0n1 CIS0n0 MD0n3 MD0n1 MD0n0

Remark n = 1

Loading...

Loading...