RL78/G10 CHAPTER 6 TIMER ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 179

Dec 22, 2016

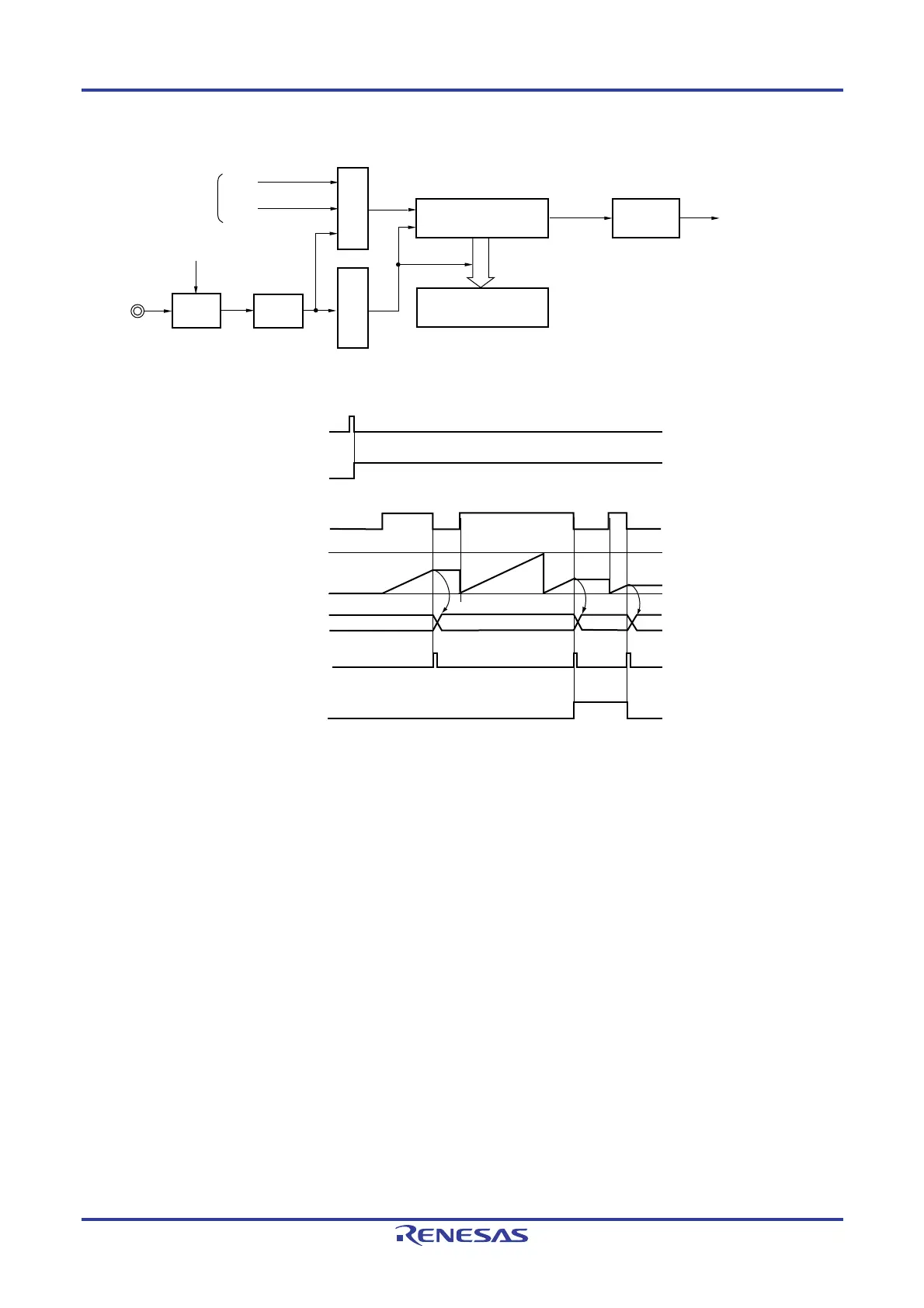

Figure 6-56. Block Diagram of Operation as Input Signal High-/Low-Level Width Measurement

Interrupt signal

(INTTM0n)

Interrupt

controller

Clock selection

Trigger selection

Operation clock

CK00

CK01

Edge

detection

TI0n pin

Timer counter

register 0n (TCR0n)

Timer data

register 0n (TDR0n)

Noise

filter

TNFEN0n

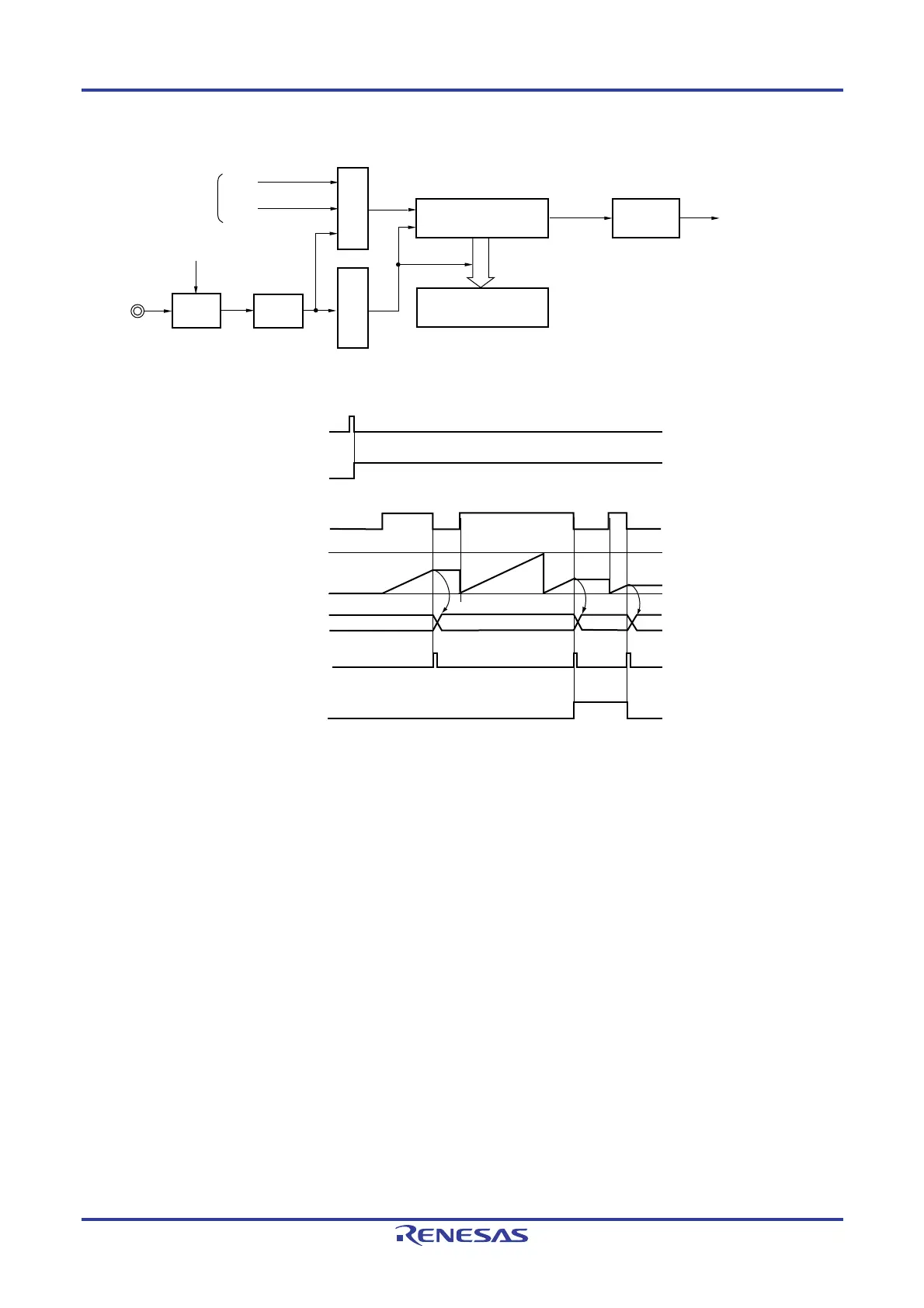

Figure 6-57. Example of Basic Timing of Operation as Input Signal High-/Low-Level Width Measurement

TS0n

TE0n

TI0n

TDR0n

TCR0n

b

0000H

a

c

INTTM0n

FFFFH

b

a

c

OVF

0000H

Remarks 1. n: Channel number

n = 0, 1 (for 10-pin products); n = 0 to 3 (for 16-pin products)

2. TS0n: Bit n of timer channel start register 0 (TS0)

TE0n: Bit n of timer channel enable status register 0 (TE0)

TI0n: TI0n pin input signal

TCR0n: Timer count register 0n (TCR0n)

TDR0n: Timer data register 0n (TDR0n)

OVF: Bit 0 of timer status register 0n (TSR0n)

Loading...

Loading...