RL78/G10 CHAPTER 10 A/D CONVERTER

R01UH0384EJ0311 Rev. 3.11 247

Dec 22, 2016

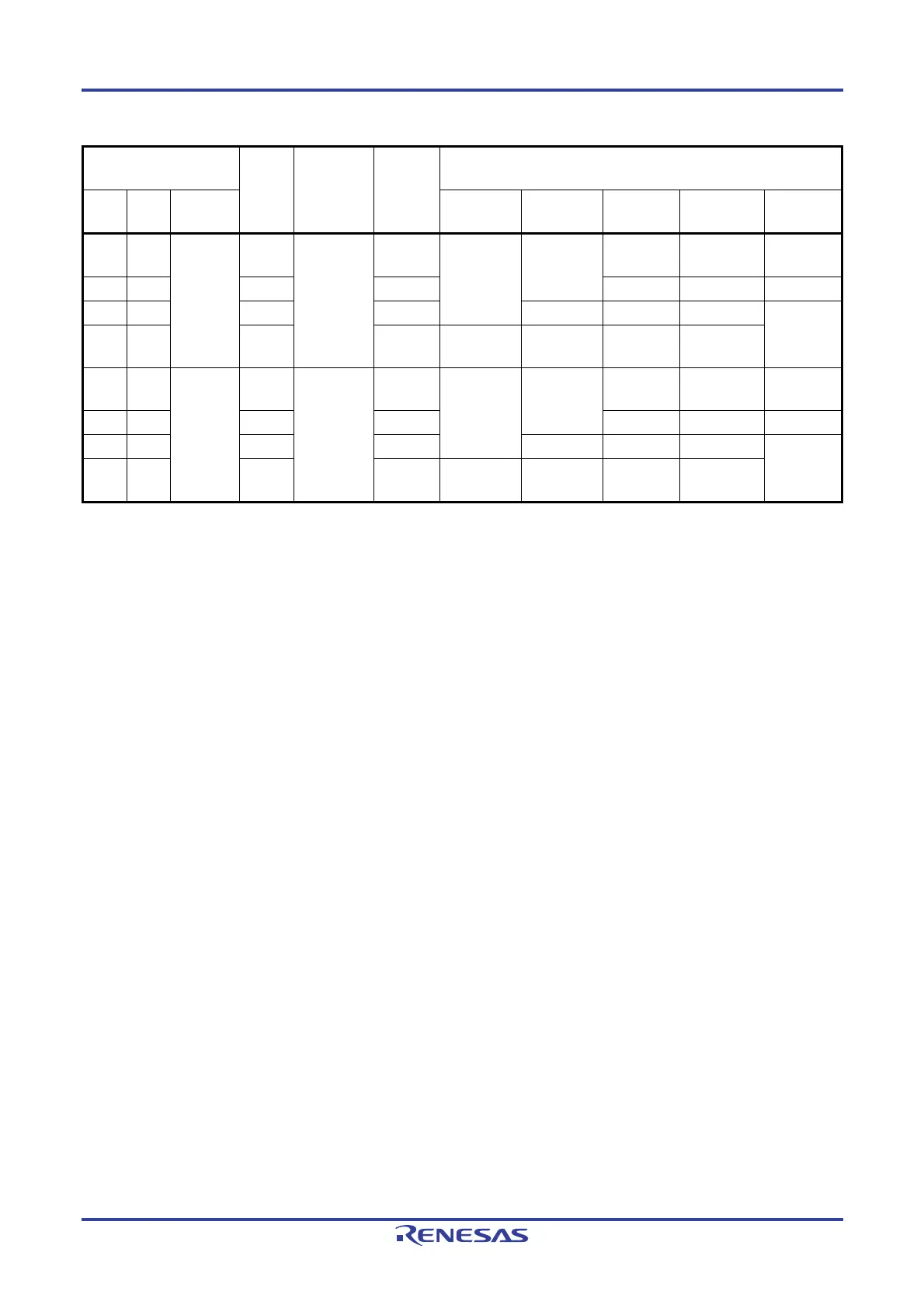

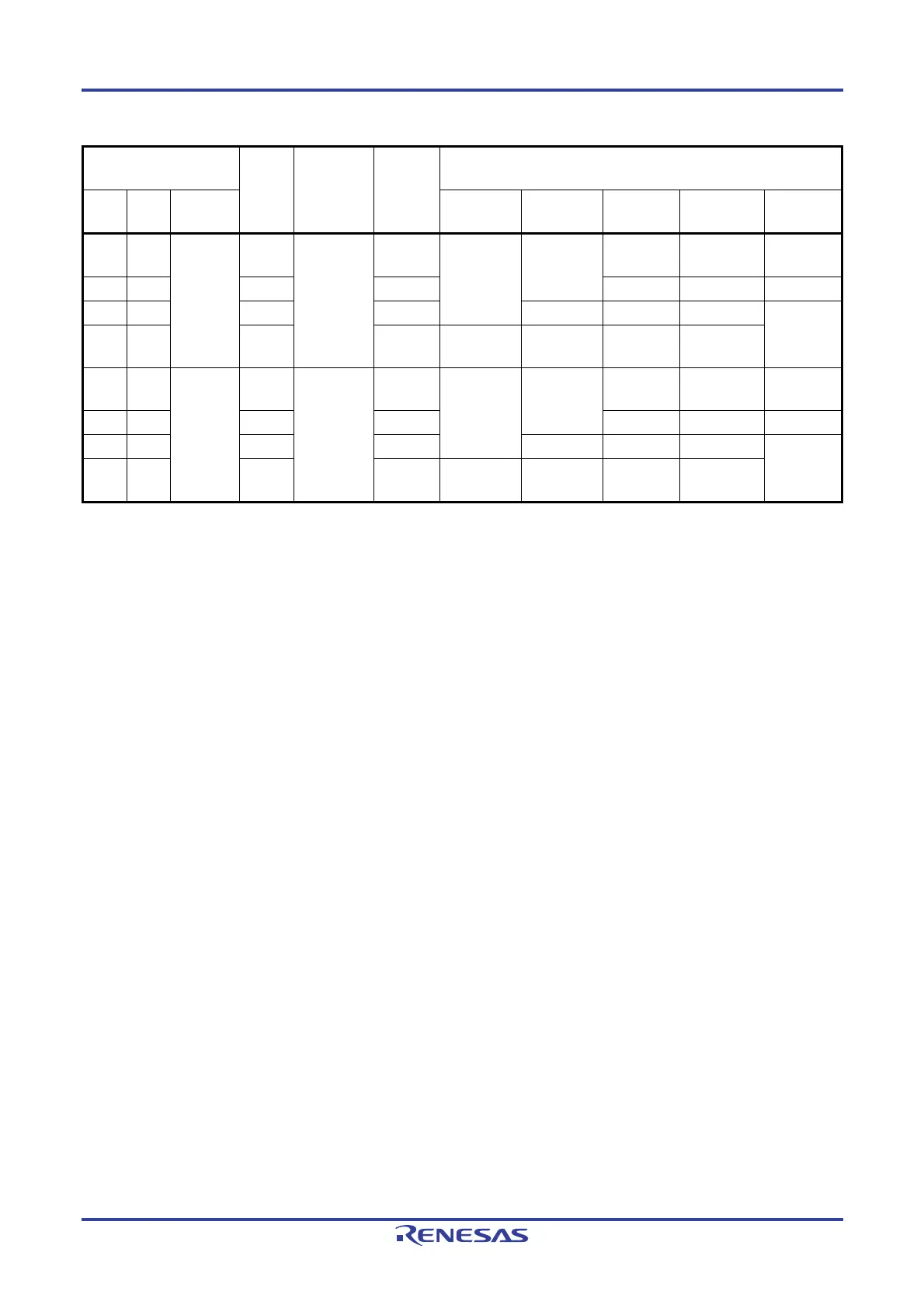

Table 10-3. 8-Bit Resolution A/D Conversion Time Selection

A/D Converter Mode

Register 0 (ADM0)

Conversion

Clock

Number of

Conversion

Clock

Conversion

Time

Conversion Time Selection (μs)

FR1 FR0 LV0

Note 2

f

CLK =

1.25 MHz

fCLK =

2.5 MHz

fCLK =

5 MHz

fCLK =

10 MHz

fCLK =

20 MHz

Note 1

0 0 0 fCLK/8 21 fAD

(Number of

sampling

clock: 9 f

AD)

168/f

CLK

Setting

prohibited

Setting

prohibited

Setting

prohibited

16.8 8.4

0 1 fCLK/4 84/fCLK 16.8 8.4 4.2

1 0 fCLK/2 42/fCLK 16.8 8.4 4.2

Setting

prohibited

1 1 fCLK 21/fCLK 16.8 8.4 4.2

Setting

prohibited

0 0 1

Note 1

fCLK/8 15 fAD

(Number of

sampling

clock: 3

f

AD)

120/f

CLK

Setting

prohibited

Setting

prohibited

Setting

prohibited

12.0 6.0

0 1 fCLK/4 60/fCLK 12.0 6.0 3.0

1 0 fCLK/2 30/fCLK 12.0 6.0 3.0

Setting

prohibited

1 1 fCLK 15/fCLK 12.0 6.0 3.0

Setting

prohibited

Notes 1. Setting prohibited when 2.4 V ≤ V

DD < 2.7 V. Can be selected when 2.7 V ≤ VDD ≤ 5.5 V.

2. When the internal reference voltage is selected as the target for conversion by the A/D converter, be sure

to clear the LV0 bit to 0.

Cautions 1. The A/D conversion time must also be within the relevant range of conversion times (tCONV)

described in 24.6.1 A/D converter characteristics.

2. When the internal reference voltage is selected as the target for conversion by the A/D converter,

the internal reference voltage cannot be used as the reference voltage of the comparator.

3. Rewrite the values of the FR1, FR0, and LV0 bits to other than the same data in the conversion

standby status (ADCS = 0, ADCE = 1) or in the conversion stopped status (ADCS = 0, ADCE = 0).

Rewriting the values of the FR1, FR0, and LV0 bits, and ADCS bits by an 8-bit manipulation

instruction at the same time is prohibited.

4. The above conversion time does not include clock frequency errors. Select conversion time,

taking clock frequency errors into consideration.

Remark f

CLK: CPU/peripheral hardware clock frequency

Loading...

Loading...