RL78/G10 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 377

Dec 22, 2016

(1) Register setting

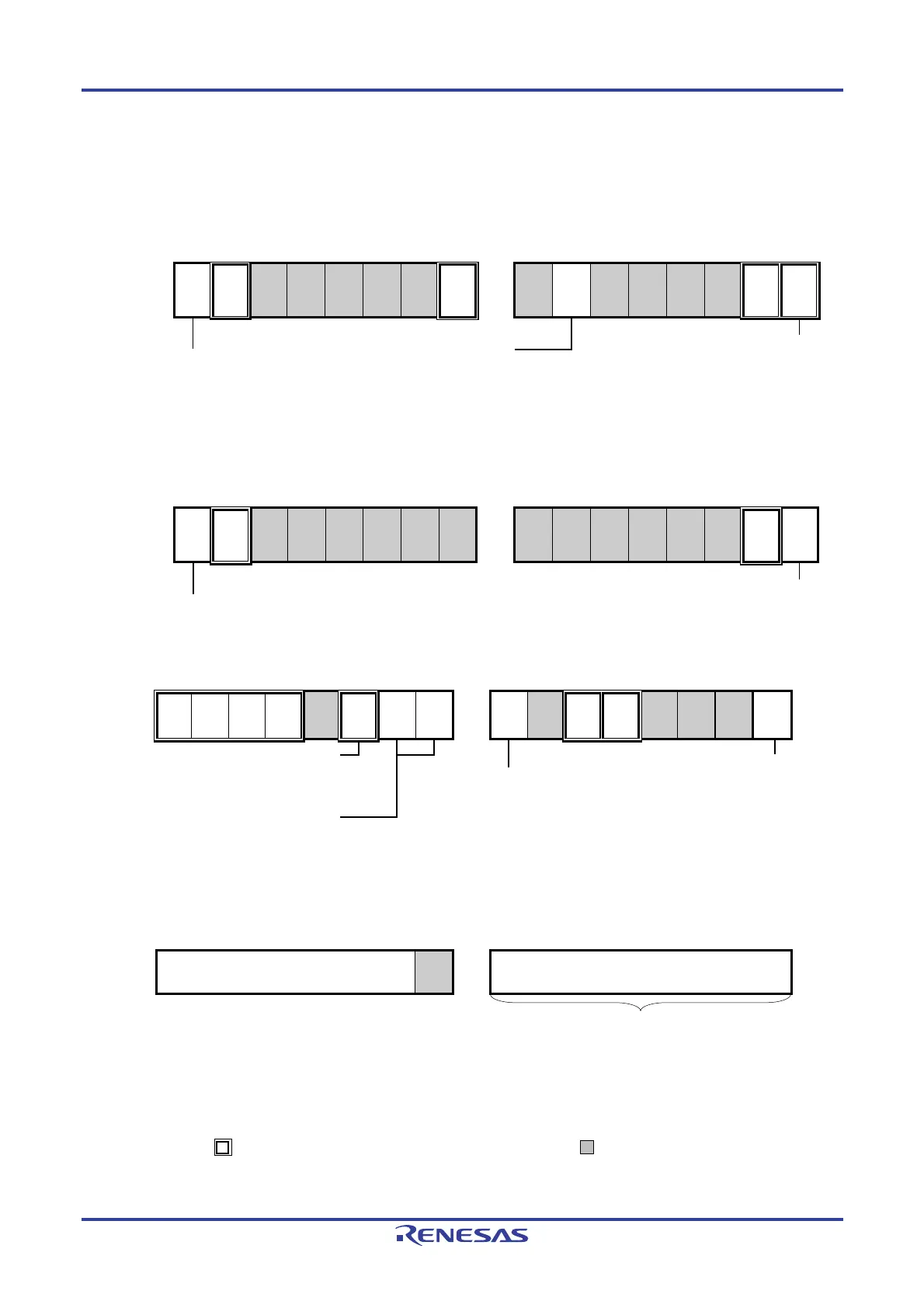

Figure 12-77. Example of Contents of Registers for UART Reception (UART0) (1/2)

(a) Serial mode register 0n (SMR0nH, SMR0nL)

Symbol: SMR0nH Symbol: SMR0nL

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CKS0n

0/1

CCS0n

0

0

0

0

0

0

STS0n

1

0

SIS0n0

0/1

1

0

0

0

MD0n1

1

MD0n0

0

0: Normal reception

1: Inverted reception

Operation mode of channel n

0: Transfer end interrupt

Operation clock (fMCK) of channel n

0: Prescaler output clock CK00

set by the SPS0 register

1: Prescaler output clock CK01

set by the SPS0 register

(b) Serial mode register 0r (SMR0rH, SMR0rL)

Symbol: SMR0rH Symbol: SMR0rL

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CKS0r

0/1

CCS0r

0

0

0

0

0

0

0

0

0

1

0

0

0

MD0r1

0

MD0r0

0/1

Operation mode of channel r

0: Transfer end interrupt

1: Buffer empty interrupt

Same setting value as CKS0n bit

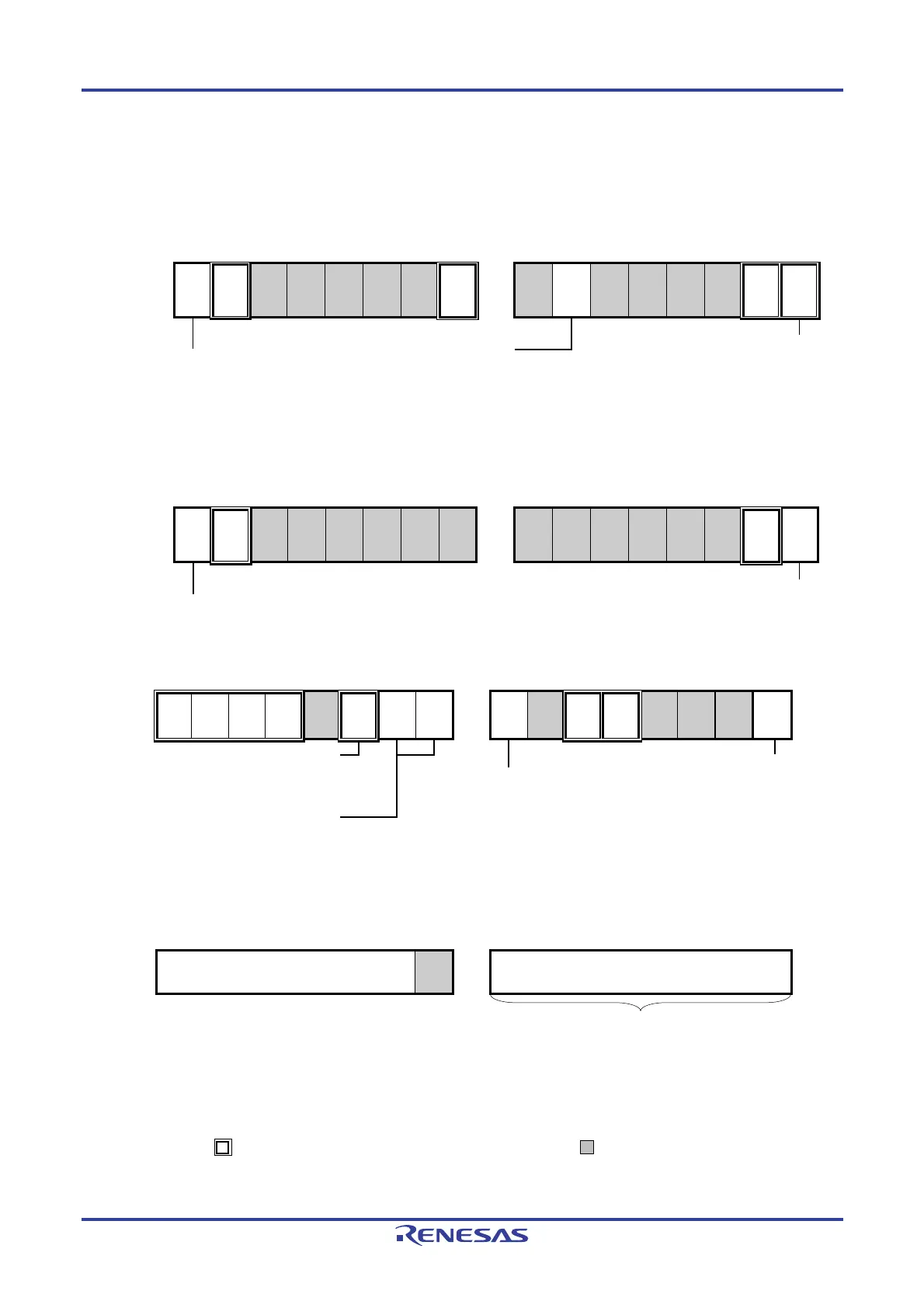

(c) Serial communication operation setting register 0n (SCR0nH, SCR0nL)

Symbol: SCR0nH Symbol: SCR0nL

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

TXE0n

0

RXE0n

1

DAP0n

0

CKP0n

0

0

EOC0n

0/1

PTC0n1

0/1

PTC0n0

0/1

DIR0n

0/1

0

SLC0n1

0

SLC0n0

1

0

1

1

DLS0n0

0/1

Masking of error interrupt INTSREx

0: Masks INTSREx

1: Enables generation of INTSREx

Setting of data length

Selection of data transfer sequence

0: Inputs/outputs data with MSB first

1: Inputs/outputs data with LSB first.

Setting of parity bit

00B: No parity

01B: No parity judgment

10B: Appending Even parity

11B: Appending Odd parity

(d) Serial data register 0n (SDR0nH, SDR0nL)

Symbol: SDR0nH Symbol: SDR0nL

7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0

Baud rate setting

0

Receive data register

Caution For UART reception, be sure to set the SMR0r register of channel r that is to be paired with channel

n.

Remarks 1. n: Channel number (n = 1),

r: Channel number (r = n - 1) q: UART number (q = 0)

2. : Setting is fixed in the UART master transmission mode, : Setting disabled (set to the initial

value)

0/1: Set to 0 or 1 depending on the usage of the user

RXD0

Loading...

Loading...