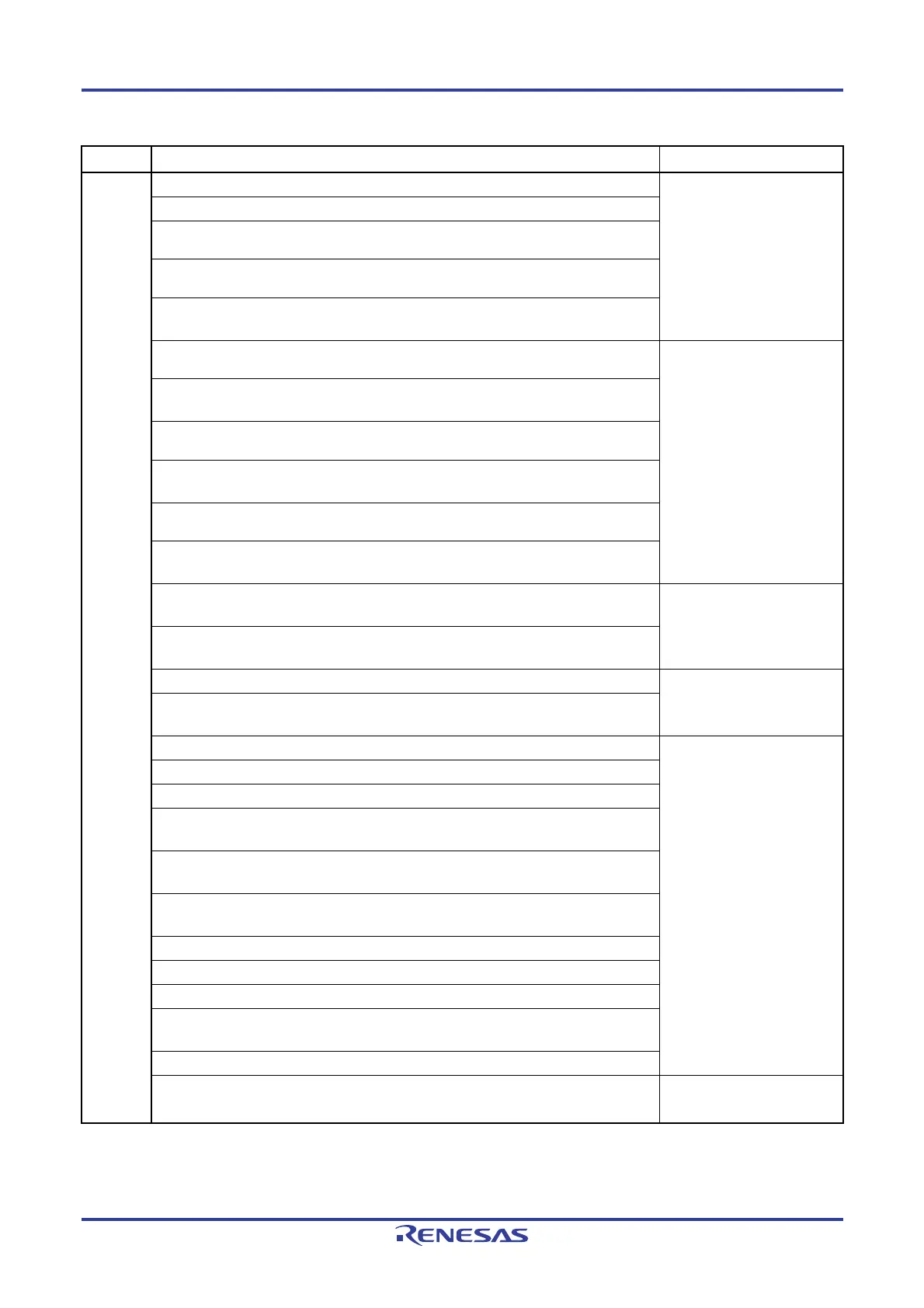

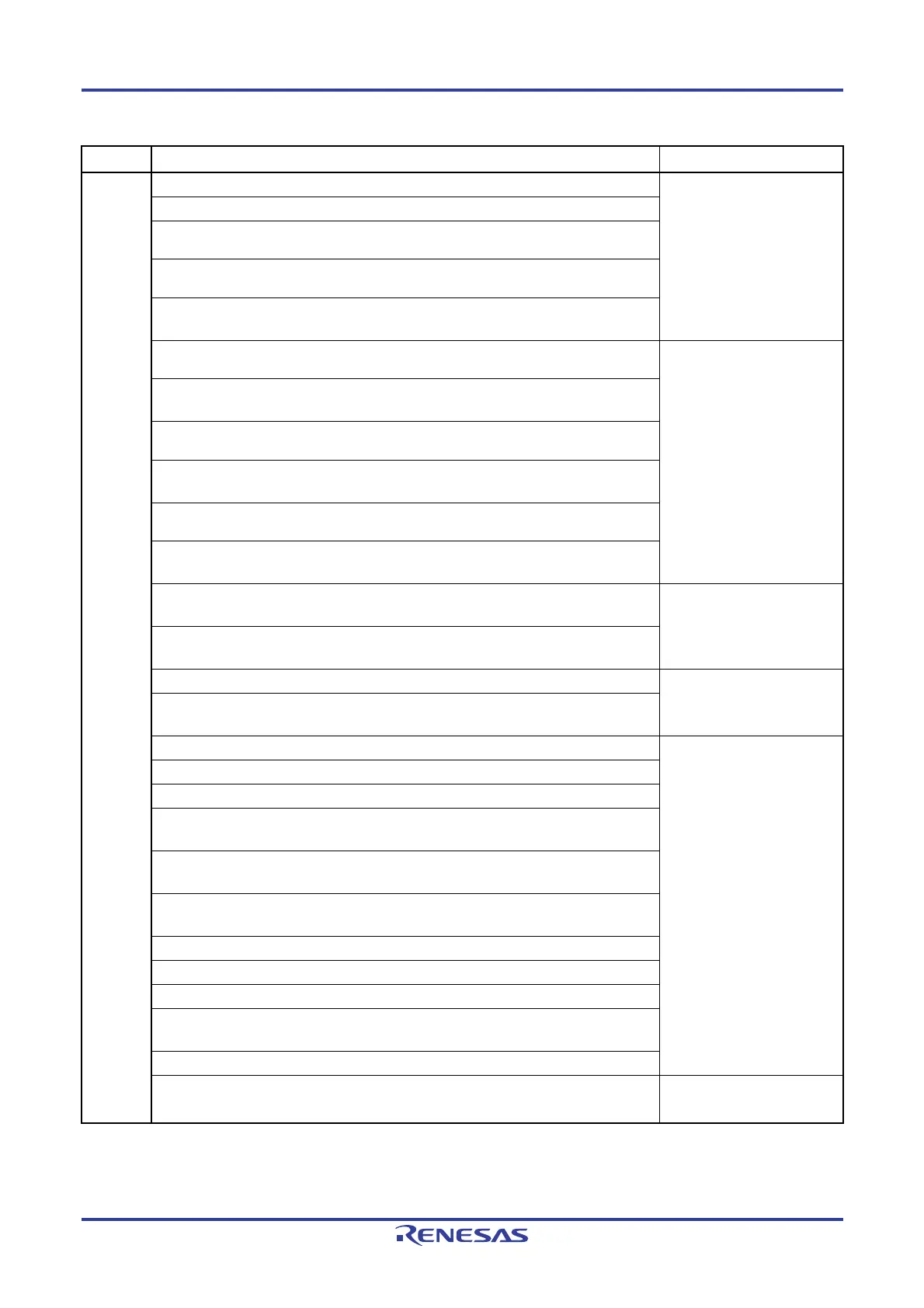

RL78/G10 APPENDIX A REVISION HISTORY

R01UH0384EJ0311 Rev. 3.11 612

Dec 22, 2016

(4/9)

Edition

Description Chapter

Rev.2.00

Modification of description in Figure 6-68 Procedure for Outputting One-Shot Pulse

CHAPTER 6

TIMER ARRAY UNIT

Addition of description in 6.9.2 Two-channel input with one-shot pulse output function

Modification of description in Figure 6-78 Procedure for Using PWM Output Function

Modification of description in 6.9.4 Operation as multiple PWM output function

Modification of description in Figure 6-83 Procedure for Using Multiple PWM Output

Function (Output Two Types of PWMs)

Modification of description in Figure 7-1 Block Diagram of 12-bit Interval Timer

CHAPTER 7

12-BIT INTERVAL TIMER

Modification of cautions 1 and 3 in Figure 7-2 Format of Peripheral Enable Register 0

(PER0)

Modification of description in 7.3.3 Interval timer control register (ITMCH, ITMCL)

Modification of description and cautions 1 to 4 in Figure 7-4 Format of Interval Timer

Control Register (ITMCH, ITMCL)

Modification of description in Figure 7-5 12-bit Interval Timer Operation Timing

Modification of description in 7.4.2 Start of count operation and re-enter to HALT/STOP

mode after returned from HALT/STOP mode

Addition of 16-pin products in Figure 8-1 Block Diagram of Clock Output/Buzzer Output

Controller

CHAPTER 8

CLOCK OUTPUT/BUZZER

OUTPUT CONTROLLER

Modification of description in 8.3.2 Registers controlling port functions of clock

output/buzzer output pin

Modification of description in Figure 9-1 Block Diagram of Watchdog Timer

CHAPTER 9

WATCHDOG TIMER

9.4.2 Setting overflow time of watchdog timer was modified to 9.4.2 Setting time of

watchdog timer

Addition of description and note

CHAPTER 10

A/D CONVERTER

Modification of description in Figure 10-1 Block Diagram of A/D Converter

Addition of description in (1) ANI0 to ANI6 pins

Modification of description in Figure 10-5 A/D Converter Sampling and A/D Conversion

Timing

Modification of caution in Figure 10-7 Format of A/D Conversion Result Higher-Order Bit

Storage Register (ADCRH)

Addition of note 2 and modification of cautions 1 to 4 in Figure 10-10 Format of Analog

Input Channel Specification Register (ADS)

Addition of description in 10.3.7 A/D test register (ADTES)

Addition of description in 10.3.8 Registers controlling port function of analog input pins

Modification of description in Figure 10-12 Conversion Operation of A/D Converter

Addition of description and figure in 10.7.2 Setting up A/D conversion of the internal

reference voltage (16-pin products only)

Modification of description in 10.9.3 Conflicting operations

Addition of description

CHAPTER 11

COMPARATOR

Loading...

Loading...