Direct memory access controller (DMA) RM0401

168/771 RM0401 Rev 3

8.3.7 Source, destination and transfer modes

Both source and destination transfers can address peripherals and memories in the entire

4 Gbytes area, at addresses comprised between 0x0000 0000 and 0xFFFF FFFF.

The direction is configured using the DIR[1:0] bits in the DMA_SxCR register and offers

three possibilities: memory-to-peripheral, peripheral-to-memory or memory-to-memory

transfers. Table 31 describes the corresponding source and destination addresses.

When the data width (programmed in the PSIZE or MSIZE bits in the DMA_SxCR register)

is a half-word or a word, respectively, the peripheral or memory address written into the

DMA_SxPAR or DMA_SxM0AR/M1AR registers has to be aligned on a word or half-word

address boundary, respectively.

Peripheral-to-memory mode

Figure 25 describes this mode.

When this mode is enabled (by setting the bit EN in the DMA_SxCR register), each time a

peripheral request occurs, the stream initiates a transfer from the source to fill the FIFO.

When the threshold level of the FIFO is reached, the contents of the FIFO are drained and

stored into the destination.

The transfer stops once the DMA_SxNDTR register reaches zero, when the peripheral

requests the end of transfers (in case of a peripheral flow controller) or when the EN bit in

the DMA_SxCR register is cleared by software.

In direct mode (when the DMDIS value in the DMA_SxFCR register is ‘0’), the threshold

level of the FIFO is not used: after each single data transfer from the peripheral to the FIFO,

the corresponding data are immediately drained and stored into the destination.

The stream has access to the AHB source or destination port only if the arbitration of the

corresponding stream is won. This arbitration is performed using the priority defined for

each stream using the PL[1:0] bits in the DMA_SxCR register.

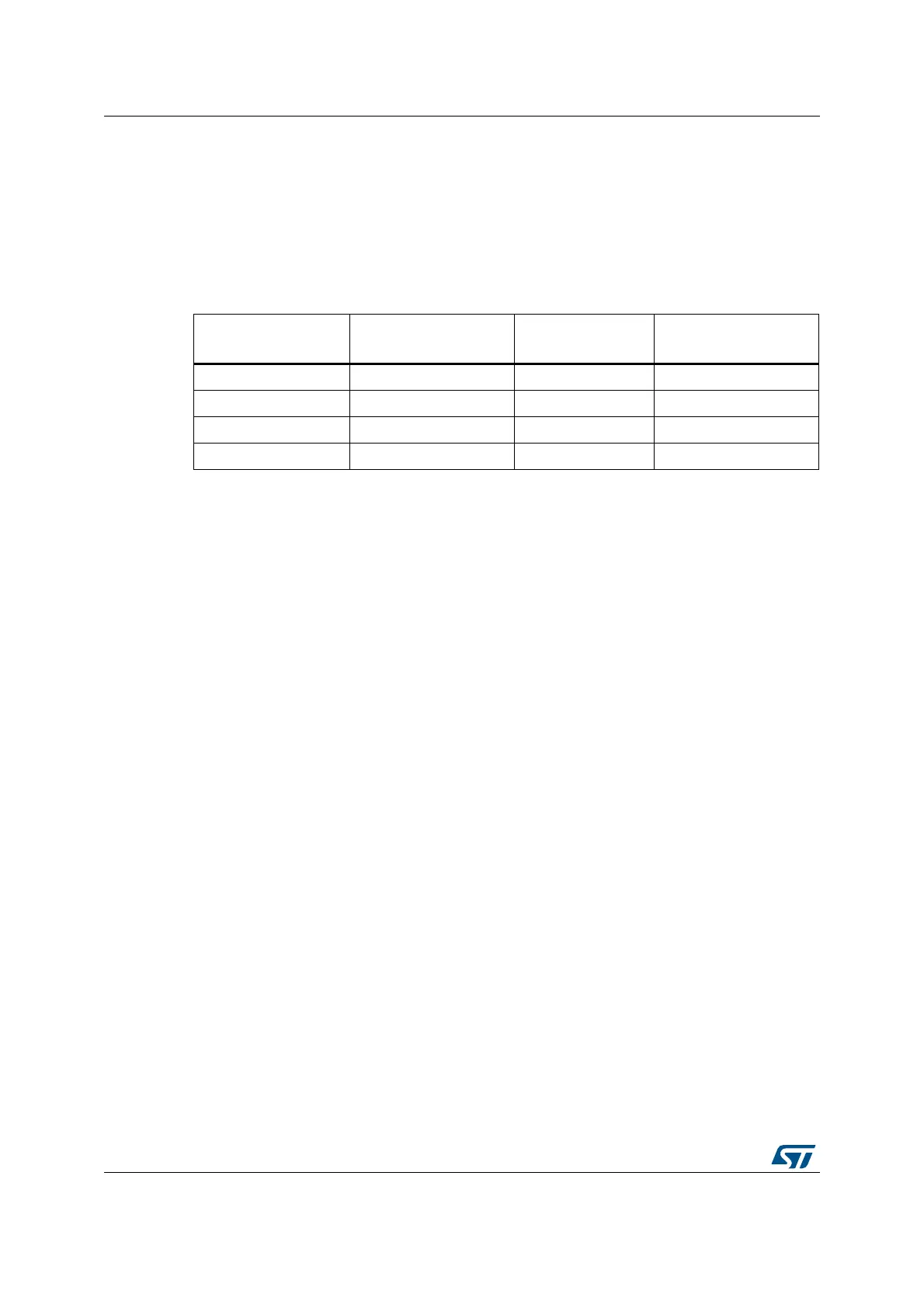

Table 31. Source and destination address

Bits DIR[1:0] of the

DMA_SxCR register

Direction Source address Destination address

00 Peripheral-to-memory DMA_SxPAR DMA_SxM0AR

01 Memory-to-peripheral DMA_SxM0AR DMA_SxPAR

10 Memory-to-memory DMA_SxPAR DMA_SxM0AR

11 Reserved - -

Loading...

Loading...