RM0401 Rev 3 79/771

RM0401 Power controller (PWR)

90

4.3.7 Stop mode

The Stop mode is based on the Cortex

®

-M4 with FPU deepsleep mode combined with

peripheral clock gating. The voltage regulator can be configured either in normal or low-

power mode. In Stop mode, all clocks in the 1.2

V domain are stopped, the PLLs, the HSI

and the HSE RC oscillators are disabled. Internal SRAM and register contents are

preserved.

Some settings in the PWR_CR register allow to further reduce the power consumption.

When the Flash memory is in power-down mode, an additional startup delay is incurred

when waking up from Stop mode (see

Table 19: Stop operating modes and Section 4.4.1:

PWR power control register (PWR_CR)).

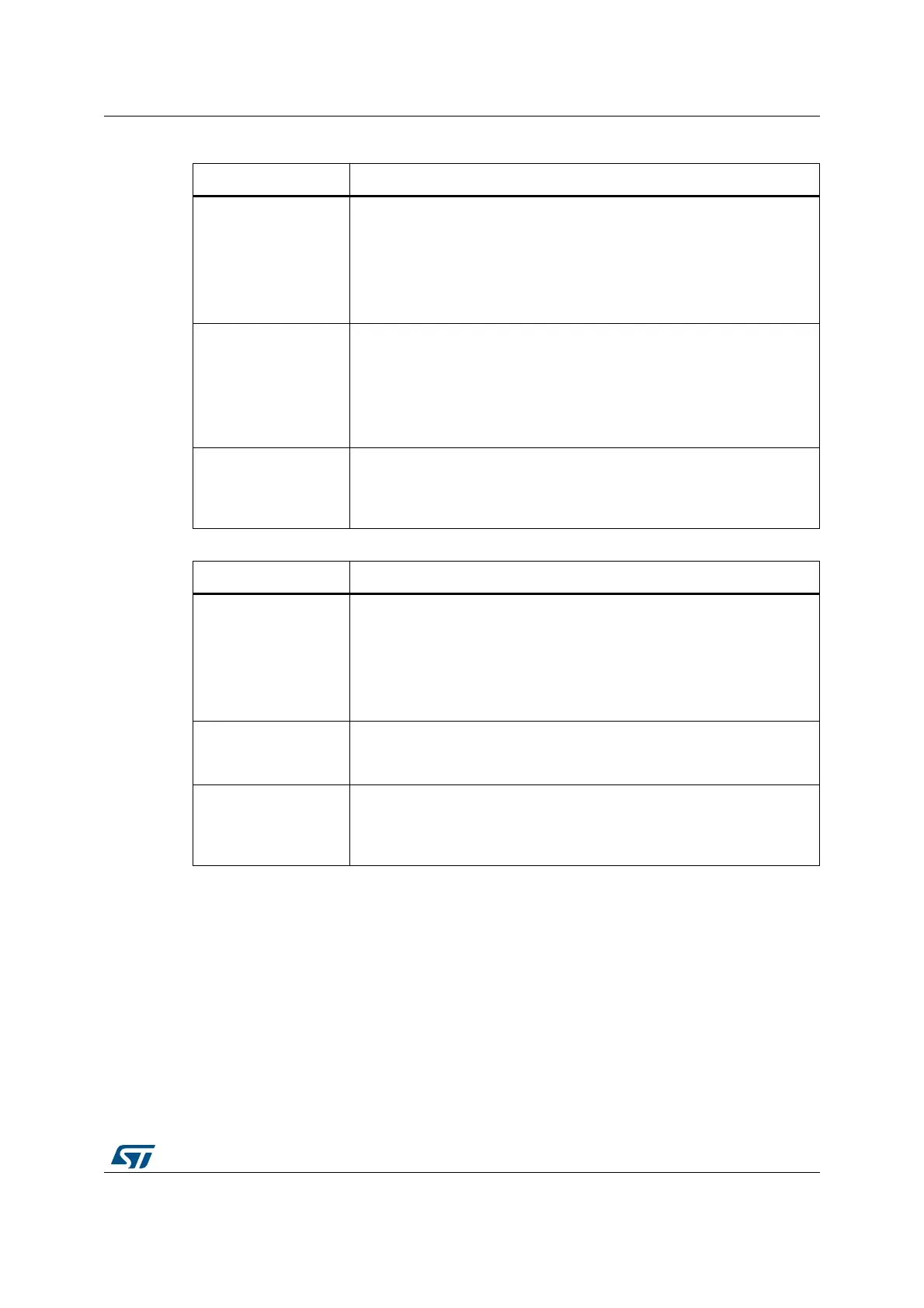

Table 17. BAM-now entry and exit

Sleep-now mode Description

Mode entry

Set the Flash memory in low-power mode:

– FISSR/FMSSR and FPDS bits of the PWR_CR register

WFI (Wait for Interrupt) or WFE (Wait for Event) while:

– SLEEPDEEP = 0 and

– SLEEPONEXIT = 0

Refer to the Cortex

®

-M4 with FPU System Control register.

Mode exit

If WFI was used for entry:

Interrupt: Refer to Table 39: Vector table

If WFE was used for entry

Wakeup event: Refer to Section 9.2.3: Wakeup event management

If Flash memory wakeup time is needed, FISSR/FMSSR bits of PWR_CR

register must be set

Wakeup latency

None if code executed from RAM

Low-power mode Flash memory wakeup time, before restarting code

execution from Flash memory (refer to the Flash memory wakeup time in

the Electrical characteristics section of the datasheet).

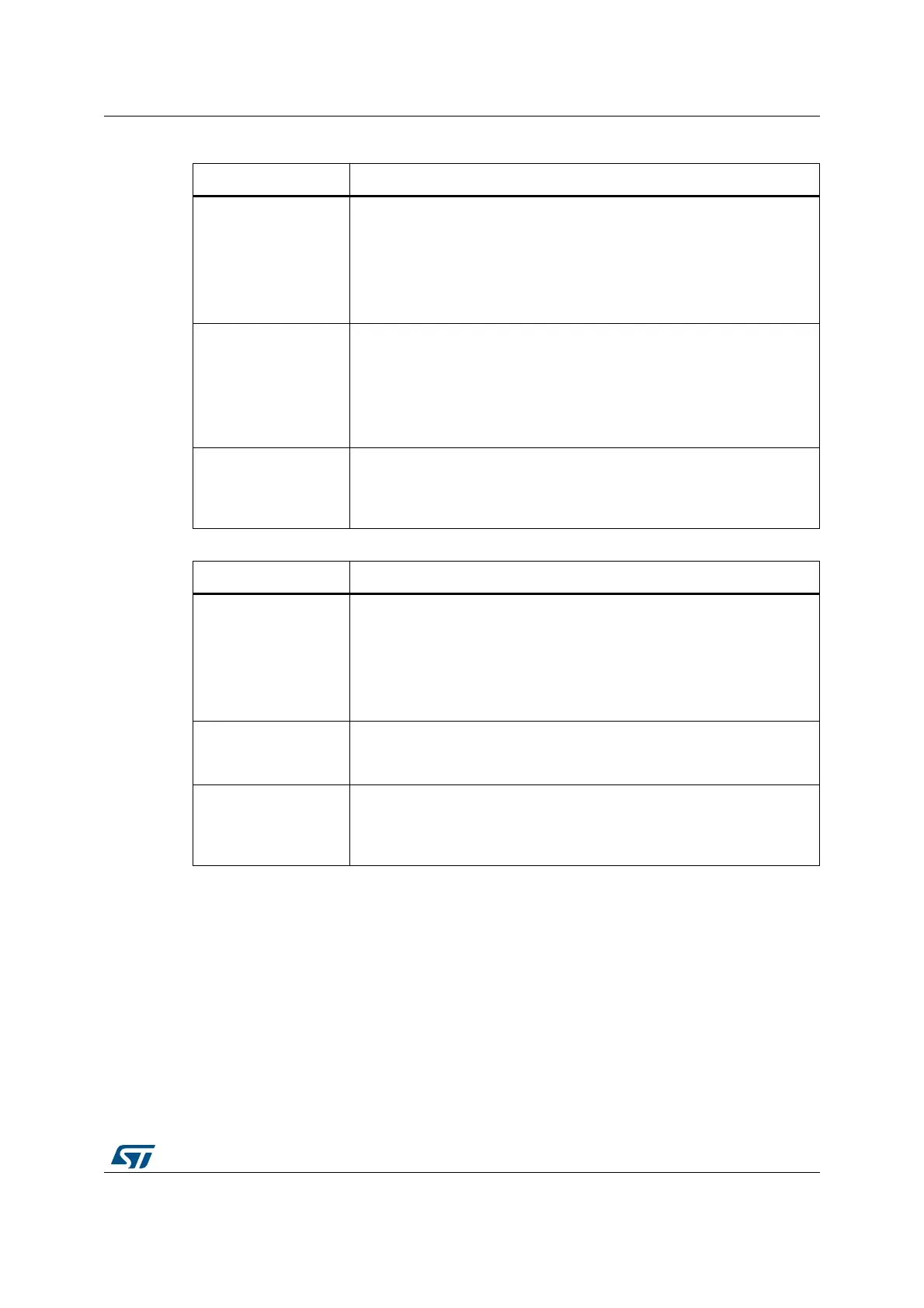

Table 18. BAM-on-exit entry and exit

Sleep-on-exit Description

Mode entry

Set the Flash memory in low-power mode:

– FISSR/FMSSR and FPDS bits of the PWR_CR register

WFI (wait for interrupt) while:

– SLEEPDEEP = 0 and

– SLEEPONEXIT = 1

Refer to the Cortex

®

-M4 with FPU System Control register.

Mode exit

Interrupt: refer to Table 39: Vector table

If Flash memory wakeup time is needed, FISSR/FMSSR bits of PWR_CR

register must be set

Wakeup latency

None when code executed from internal SRAM

Low-power mode Flash memory wakeup time, before restarting code

execution from Flash memory (refer to the Flash memory wakeup time in

the Electrical characteristics section of the datasheet).

Loading...

Loading...