RM0401 Rev 3 373/771

RM0401 General-purpose timers (TIM5)

389

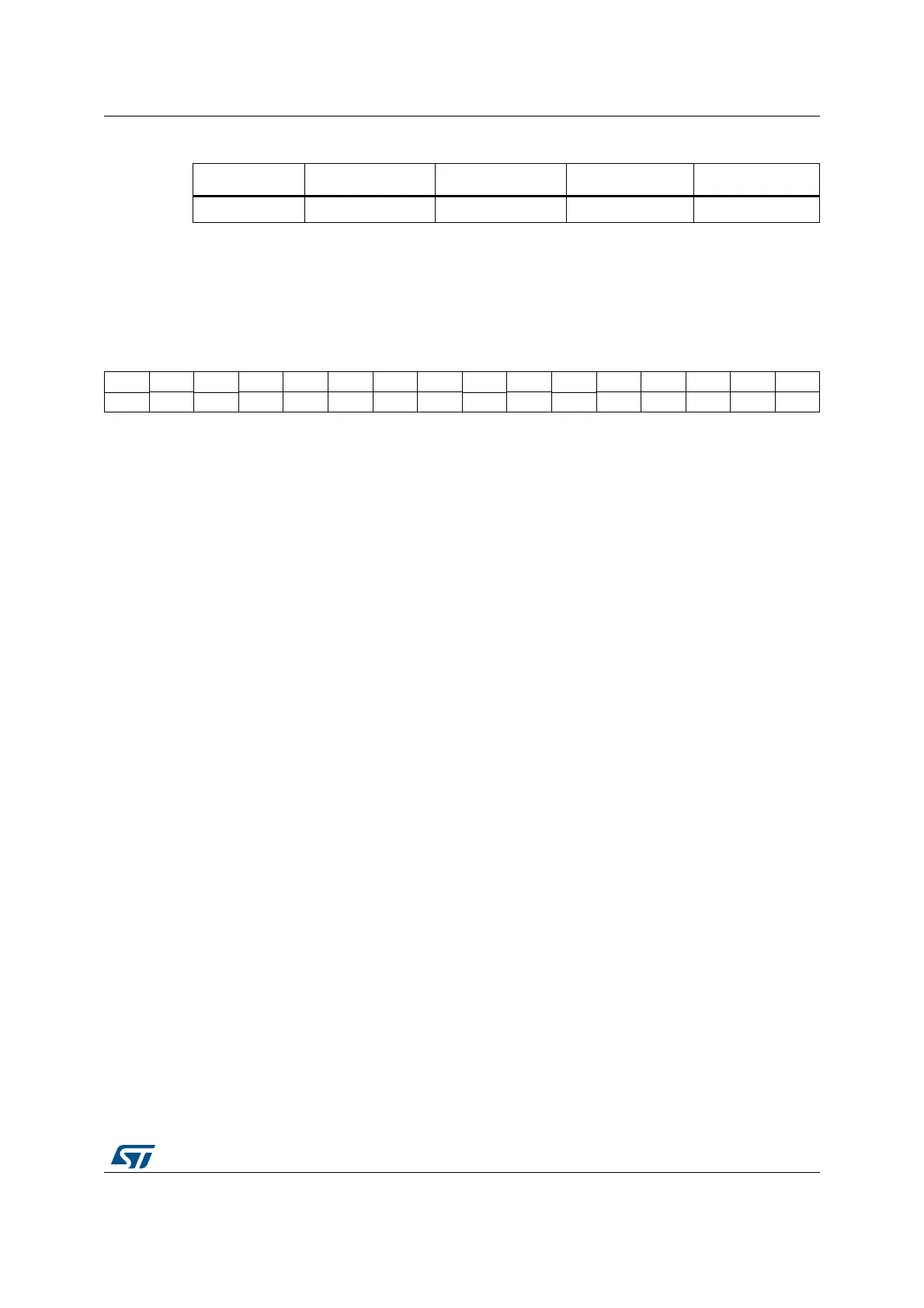

15.4.4 TIMx DMA/Interrupt enable register (TIMx_DIER)

Address offset: 0x0C

Reset value: 0x0000

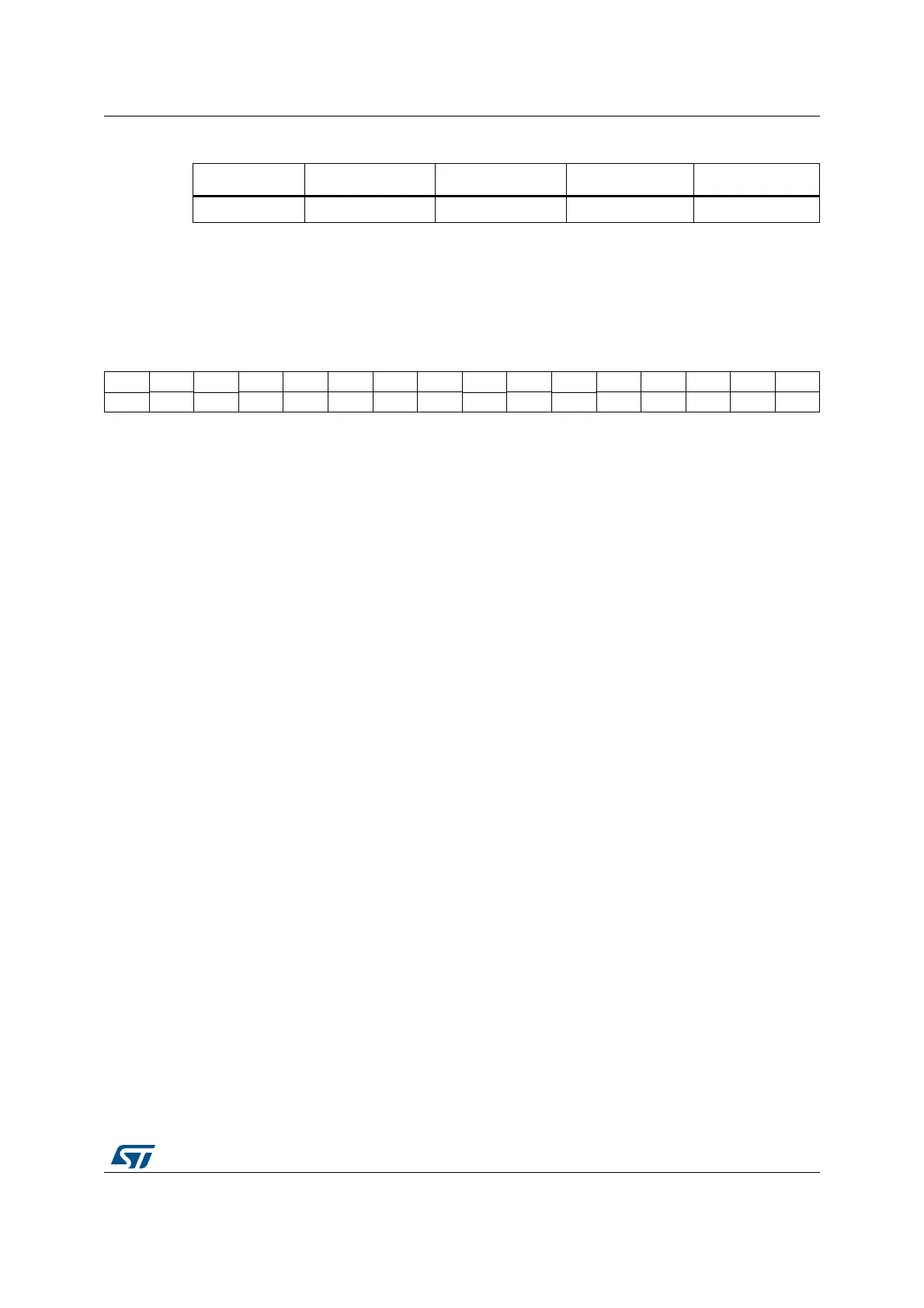

Table 62. TIMx internal trigger connection

Slave TIM ITR0 (TS = 000) ITR1 (TS = 001) ITR2 (TS = 010) ITR3 (TS = 011)

TIM5 Reserved LPTIM Reserved Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. TDE Res. CC4DE CC3DE CC2DE CC1DE UDE Res. TIE Res. CC4IE CC3IE CC2IE CC1IE UIE

rw rw rw rw rw rw rw rw rw rw rw rw

Bit 15 Reserved, must be kept at reset value.

Bit 14 TDE: Trigger DMA request enable

0: Trigger DMA request disabled.

1: Trigger DMA request enabled.

Bit 13 Reserved, always read as 0

Bit 12 CC4DE: Capture/Compare 4 DMA request enable

0: CC4 DMA request disabled.

1: CC4 DMA request enabled.

Bit 11 CC3DE: Capture/Compare 3 DMA request enable

0: CC3 DMA request disabled.

1: CC3 DMA request enabled.

Bit 10 CC2DE: Capture/Compare 2 DMA request enable

0: CC2 DMA request disabled.

1: CC2 DMA request enabled.

Bit 9 CC1DE: Capture/Compare 1 DMA request enable

0: CC1 DMA request disabled.

1: CC1 DMA request enabled.

Bit 8 UDE: Update DMA request enable

0: Update DMA request disabled.

1: Update DMA request enabled.

Bit 7 Reserved, must be kept at reset value.

Bit 6 TIE: Trigger interrupt enable

0: Trigger interrupt disabled.

1: Trigger interrupt enabled.

Bit 5 Reserved, must be kept at reset value.

Bit 4 CC4IE: Capture/Compare 4 interrupt enable

0: CC4 interrupt disabled.

1: CC4 interrupt enabled.

Bit 3 CC3IE: Capture/Compare 3 interrupt enable

0: CC3 interrupt disabled

1: CC3 interrupt enabled

Loading...

Loading...