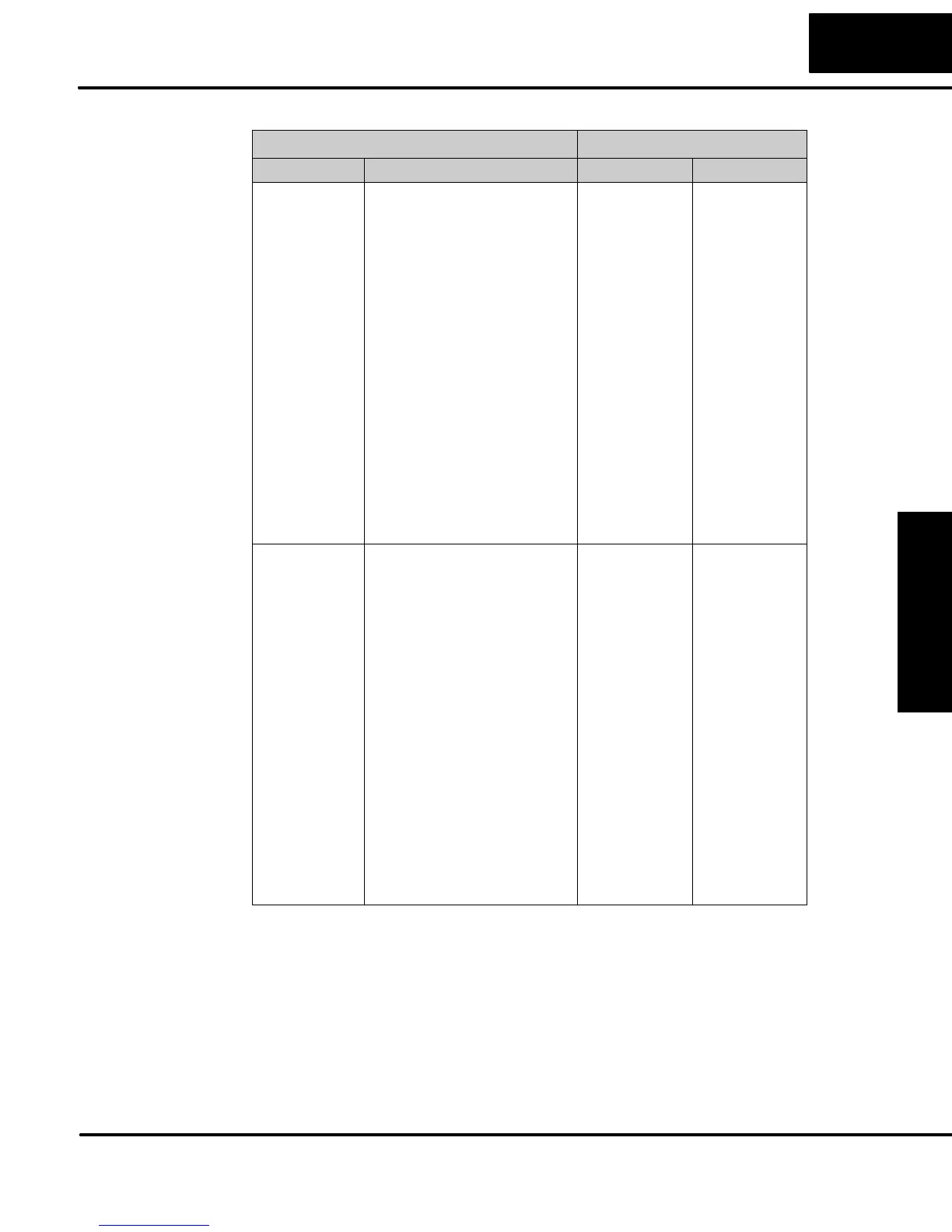

Appendix C

Inst. Execution Times

C–5

Instruction Execution Times

Comparative Boolean (cont.)

DL05

Instruct Legal Data Types Execute Not Execute

ORE 1st 2nd

V: Data Reg. V:Data Reg.

V:Bit Reg.

K:Constant

P:Indir. (Data)

P:Indir. (Bit)

V: Bit Reg. V:Data Reg.

V:Bit Reg.

K:Constant

P:Indir. (Data)

P:Indir. (Bit)

P:Indir. (Data) V:Data Reg.

V:Bit Reg.

K:Constant

P:Indir. (Data)

P:Indir. (Bit)

P:Indir. (Bit) V:Data Reg.

V:Bit Reg.

K:Constant

P:Indir. (Data)

P:Indir. (Bit)

16.6 ms

16.6 ms

11.5 m s

42.6 ms

42.6 ms

16.6 ms

16.6 ms

11.5 m s

42.6 ms

42.6 ms

37.7 ms

37.7 ms

42.6 ms

66.5 ms

66.5 ms

37.7 ms

37.7 ms

42.6 ms

66.5 ms

66.5 ms

16.5 ms

16.5 ms

11.4 ms

42.5 ms

42.5 ms

16.5 ms

16.5 ms

11.4 ms

42.5 ms

42.5 ms

37.6 ms

37.6 ms

42.5 ms

66.4 ms

66.4 ms

37.6 ms

37.6 ms

42.5 ms

66.4 ms

66.4 ms

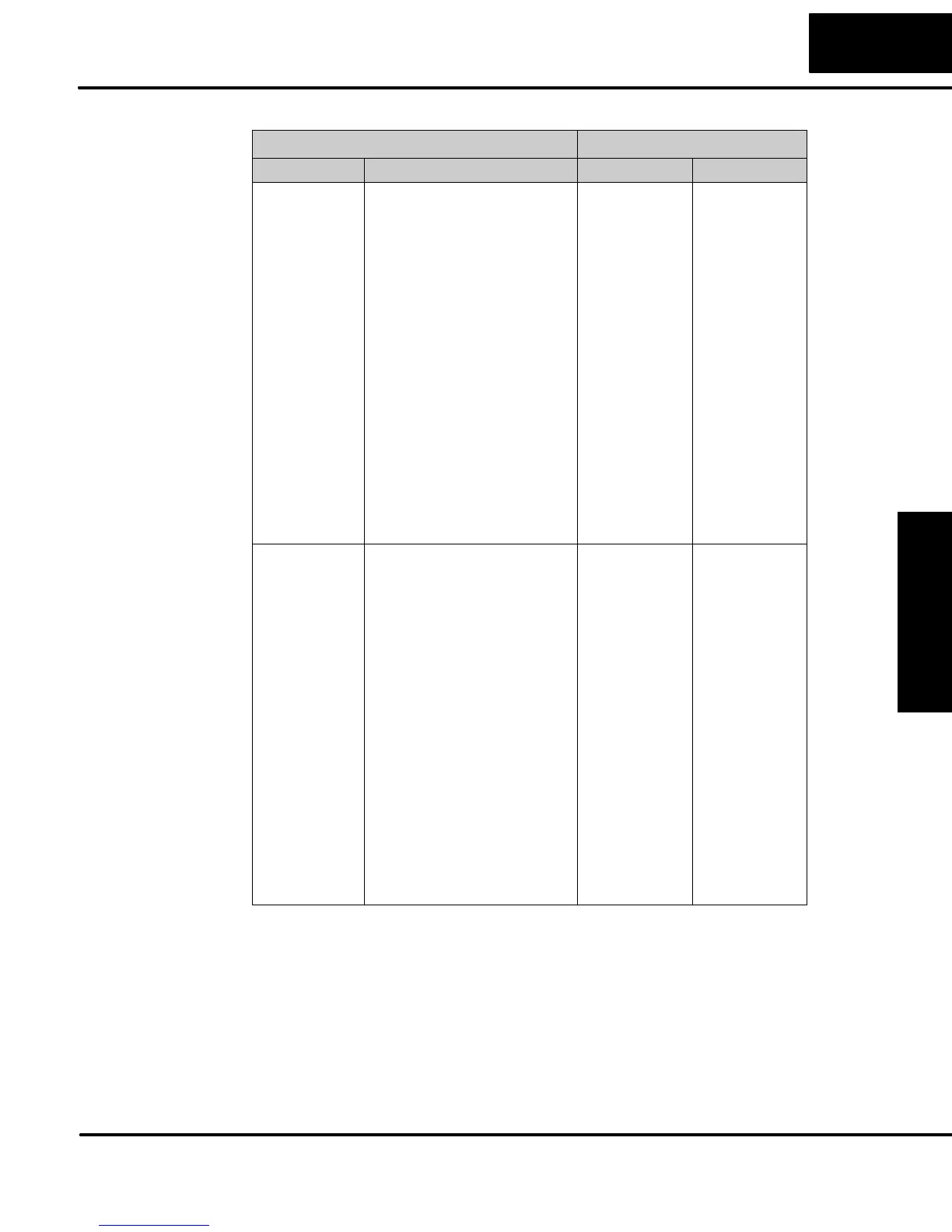

ORNE 1st 2nd

V: Data Reg. V:Data Reg.

V:Bit Reg.

K:Constant

P:Indir. (Data)

P:Indir. (Bit)

V: Bit Reg. V:Data Reg.

V:Bit Reg.

K:Constant

P:Indir. (Data)

P:Indir. (Bit)

P:Indir. (Data) V:Data Reg.

V:Bit Reg.

K:Constant

P:Indir. (Data)

P:Indir. (Bit)

P:Indir. (Bit) V:Data Reg.

V:Bit Reg.

K:Constant

P:Indir. (Data)

P:Indir. (Bit)

16.7 ms

16.7 ms

11.6 m s

42.7 ms

42.7 ms

16.7 ms

16.7 ms

11.6 m s

42.7 ms

42.7 ms

42.7 ms

42.7 ms

37.8 ms

66.6 ms

66.6 ms

42.7 ms

42.7 ms

37.8 ms

66.6 ms

66.6 ms

16.8 ms

16.8 ms

11.7 ms

42.9 ms

42.9 ms

16.8 ms

16.8 ms

11.7 ms

42.9 ms

42.9 ms

42.8 ms

42.8 ms

38.0 ms

66.7 ms

66.7 ms

42.8 ms

42.8 ms

38.0 ms

66.7 ms

66.7 ms

Loading...

Loading...