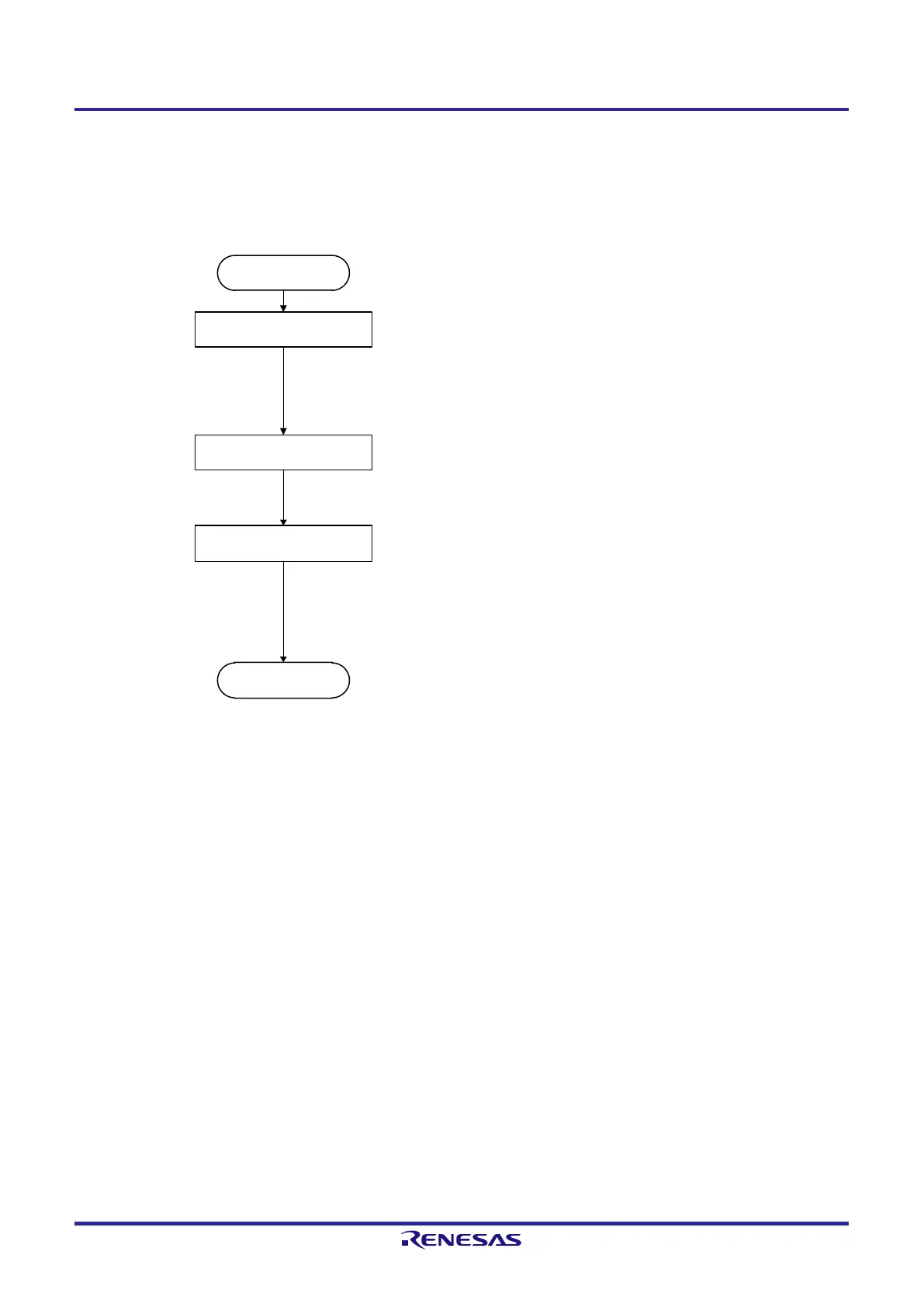

Start

Set the C0IE bit

Set the C0ENB bit

Set the PER0 register

(Mandatory)

(Mandatory)

(Optional)

End

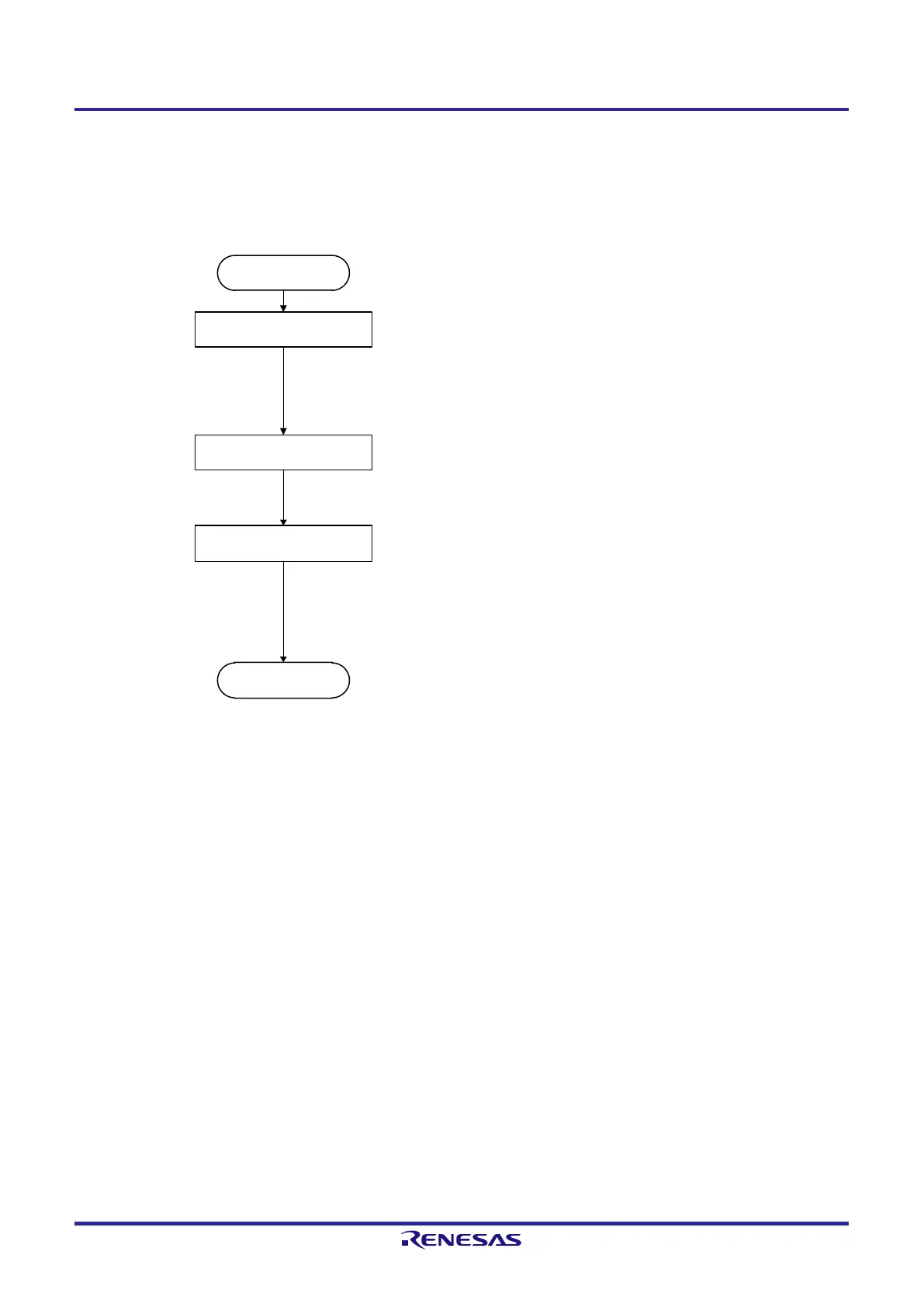

Disable comparator interrupt request.

Clear the C0IE bit in COMPOCR to 0 to disable interrupt request.

Clear the comparator interrupt request flag.

Clear the CMPIF0 bit in IF1H to 0 to initialize interrupt request

(unnecessary interrupt request cleared).

Clear the CMPEN bit in PER0 to 0 to stop clock supply to the comparator.

Note that stopping clock supply by setting PER0 initializes all control registers of

the comparator (except for port mode register 0 (PM0), port register 0 (P0), and

port mode control register 0 (PMC0)).

To use the comparator again, set the control registers according to Figure 11-8

Procedure for Enabling Comparator Operation.

Disable comparator operation.

Clear the C0ENB bit in COMPMDR to 0 to stop comparator 0 operation.

Loading...

Loading...