RL78/G15 CHAPTER 14 INTERRUPT FUNCTIONS

R01UH0959EJ0110 Rev.1.10 Page 610 of 765

Mar 7, 2023

14.3.3 Priority specification flag registers (PR00L, PR00H, PR01L, PR01H, PR10L,

PR10H, PR11L, PR11H)

The priority specification flag registers are used to set the corresponding maskable interrupt priority level.

A priority level is set by using the PR0xy and PR1xy registers in combination (xy = 0L, 0H, 1L, 1H).

The PR00L, PR00H, PR01L, PR01H, PR10L, PR10H, PR11L, and PR11H registers can be set by a 1-bit or 8-bit

memory manipulation instruction. If the PR00L and PR00H registers, the PR01L and PR01H registers, the PR10L and

PR10H registers, and the PR11L and PR11H registers are combined to form 16-bit registers PR00, PR01, PR10, and

PR11, they can be set by a 16-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

Remark If an instruction that writes data to this register is executed, the number of instruction execution clocks

increases by 2 clocks.

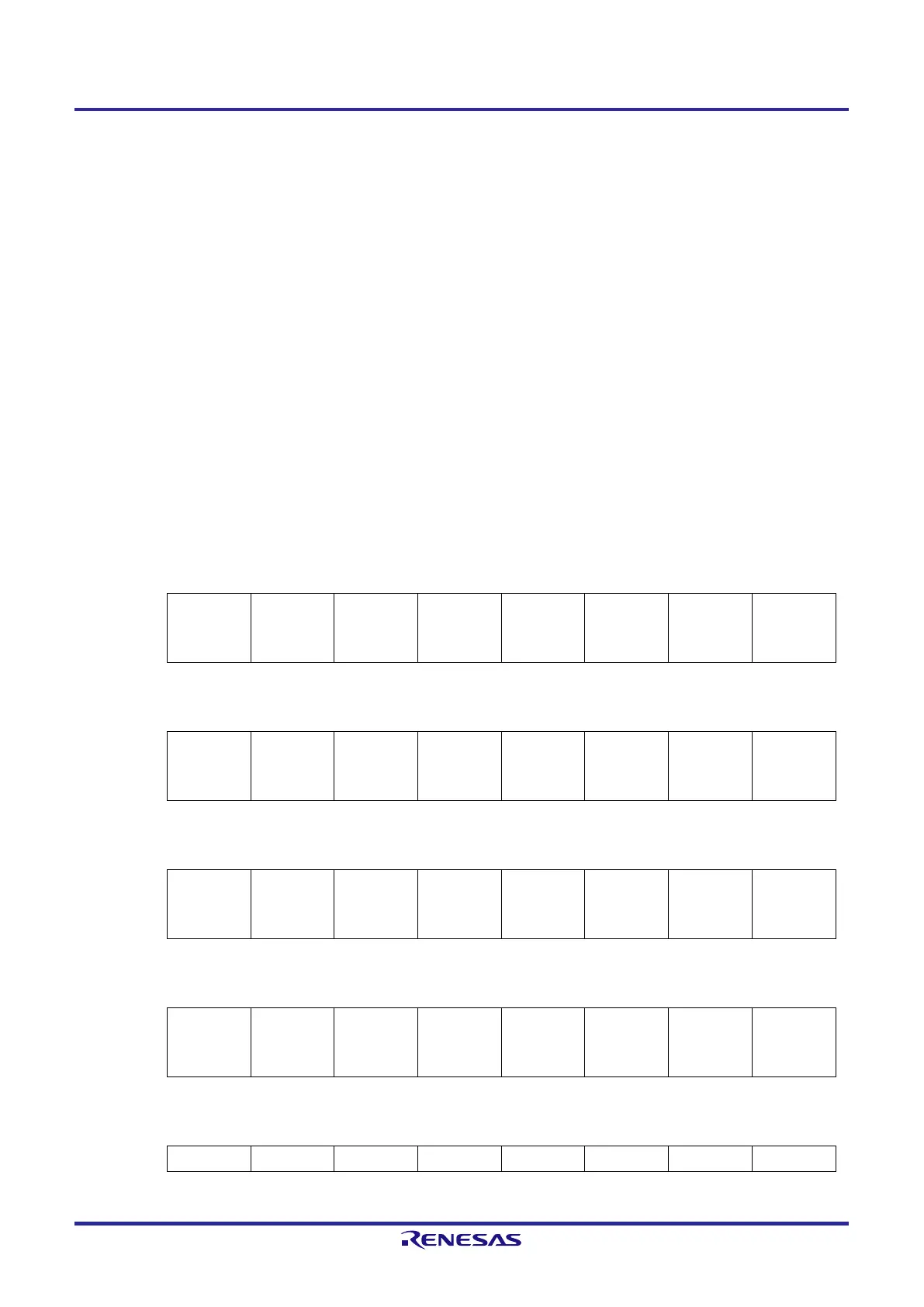

Figure 14-4. Format of Priority Specification Flag Registers

(PR00L, PR00H, PR01L, PR01H, PR10L, PR10H, PR11L, PR11H)

Address: FFFE8H After reset: FFH R/W

Symbol

□

7

□

6

□

5

□

4

□

3

□

2

□

1

□

0

PR00L STPR00

CSIPR000

IICPR000

PPR05 PPR04 PPR03 PPR02 PPR01 PPR00 WDTIPR0

Address: FFFECH After reset: FFH R/W

Symbol

□

7

□

6

□

5

□

4

□

3

□

2

□

1

□

0

PR10L STPR10

CSIPR100

IICPR100

PPR15 PPR14 PPR13 PPR12 PPR11 PPR10 WDTIPR1

Address: FFFE9H After reset: FFH R/W

Symbol

□

7

□

6

□

5

□

4

□

3

□

2

□

1

□

0

PR00H PPR07 PPR06 ADPR0 TMPR001 TMPR000 TMPR001H SREPR00 SRPR00

CSIPR001

IICPR001

Address: FFFEDH After reset: FFH R/W

Symbol

□

7

□

6

□

5

□

4

□

3

□

2

□

1

□

0

PR10H PPR17 PPR16 ADPR1 TMPR101 TMPR100 TMPR101H SREPR10 SRPR10

CSIPR101

IICPR101

Address: FFFEAH After reset: FFH R/W

Symbol

□

7

□

6

□

5

□

4

□

3

□

2

□

1

□

0

PR01L TMPR006 TMPR005 TMPR004 ITPR0 TMPR003 TMPR002 IICAPR00 TMPR003H

Loading...

Loading...