RL78/G15 CHAPTER 13 SERIAL INTERFACE IICA

R01UH0959EJ0110 Rev.1.10 Page 534 of 765

Mar 7, 2023

13.5.3 Transfer direction specification

Following the 7-bit address, the master sends 1-bit data to specify the transfer direction.

When this transfer direction specification bit is 0, it indicates that the master is transmitting data to a slave. When the

transfer direction specification bit is 1, it indicates that the master is receiving data from a slave.

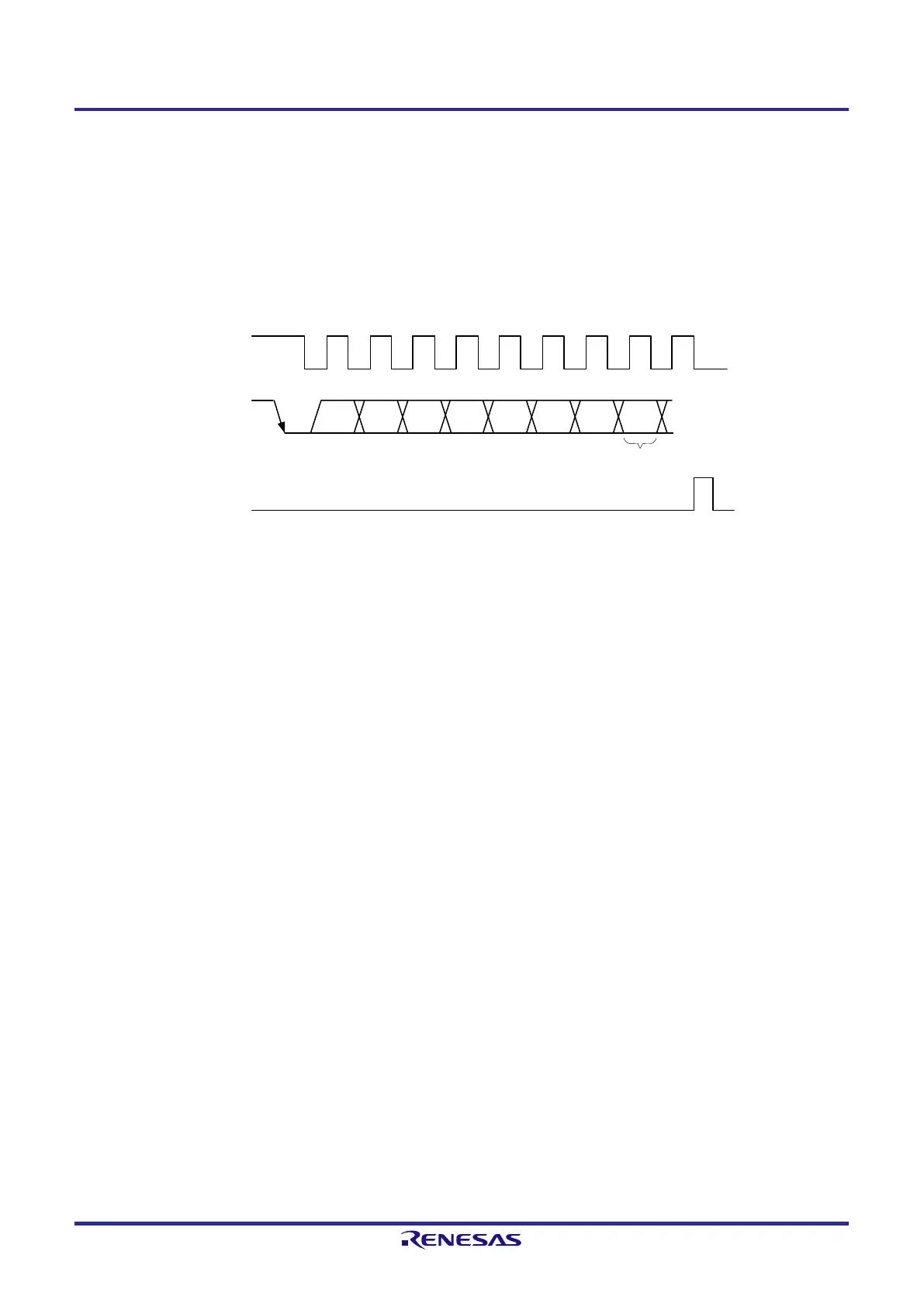

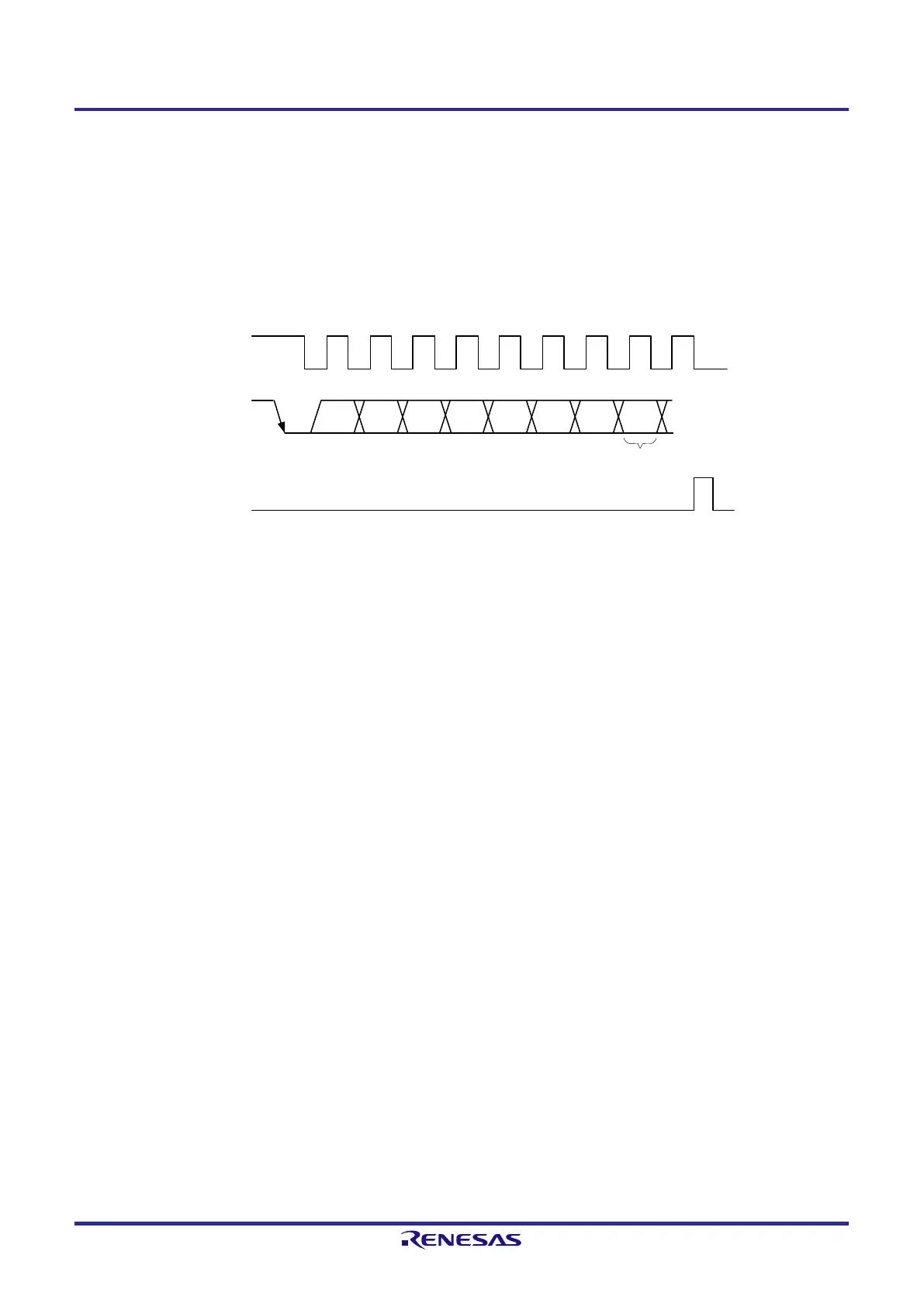

Figure 13-16. Transfer Direction Specification

SCLA0

SDAA0

INTIICA0

1 2 3 4 5 6 7 8 9

A6 A5 A4 A3 A2 A1 A0

__

R/W

Note 1

Transfer direction

specification

Note 1. INTIICA0 is not generated if data other than the local address or extension code is received in slave

operation.

13.5.4 Acknowledge (ACK)

ACK is used to check the state of serial data on the transmission and reception sides.

The reception side returns ACK each time it receives 8-bit data.

The transmission side usually receives ACK after transmitting 8-bit data. When ACK is returned from the reception side,

it is assumed that reception has been correctly performed and processing is continued. The detection of ACK can be

checked by using bit 2 (ACKD0) of IICA status register 0 (IICS0).

When the master receives the last data item, it does not return ACK but generates a stop condition. If a slave does not

return ACK in reception, the master outputs a stop condition or restart condition and stops transmission. If ACK is not

returned, the following causes can be considered.

<1> Reception was not performed normally.

<2> The final data item was received.

<3> The reception side specified by the address does not exist.

To generate ACK, the reception side sets the SDAA0 line to the low level at the 9th clock (normal reception).

Automatic generation of ACK is enabled by setting bit 2 (ACKE0) of IICA control register 00 (IICCTL00) to 1. Bit 3

(TRC0) of the IICS0 register is set by the 8th bit data that follows 7-bit address information. Usually, set the ACKE0 bit to

1 for reception (TRC0 = 0).

When the slave can no longer receive data during reception (TRC0 = 0) or does not require the next data item, the slave

must clear the ACKE0 bit to 0 to inform the master that it cannot receive any more data.

Loading...

Loading...