RL78/G15 CHAPTER 19 FLASH MEMORY

R01UH0959EJ0110 Rev.1.10 Page 677 of 765

Mar 7, 2023

19.6.1.7 Flash memory sequencer status registers H and L (FSASTH, FSASTL)

The FSASTH and FSASTL registers indicate the results of the operations of the flash memory sequencer.

The FSASTH and FSASTL registers can be read by an 8-bit memory manipulation instruction.

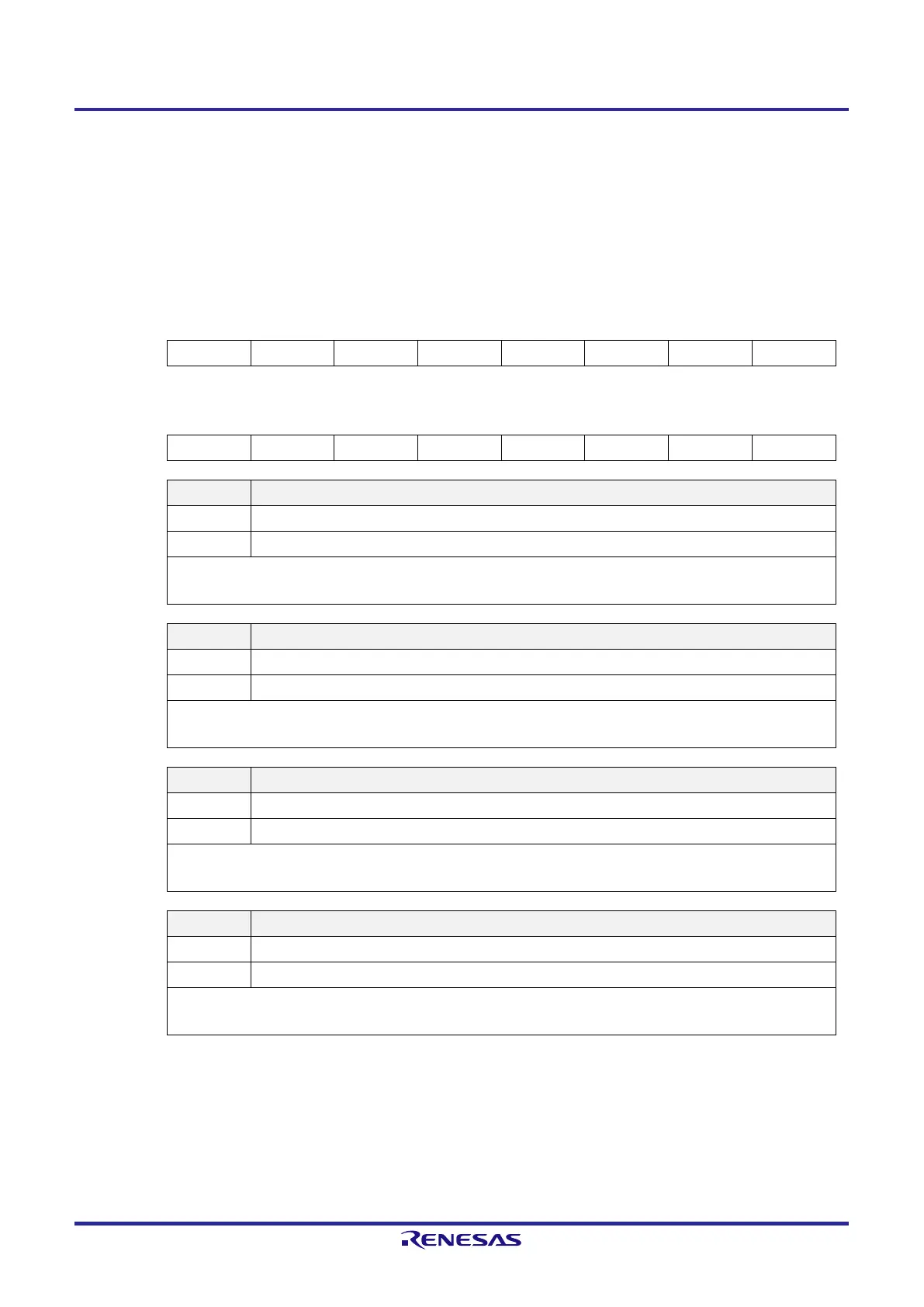

Figure 19-14. Format of Flash Memory Sequencer Status Registers H and L (FSASTH, FSASTL)

Address: F00C7H After reset: 00H R

Symbol 7 6 5 4 3 2 1 0

FSASTH 0 SQEND 0 0 0 0 0 0

Address: F00C6H After reset: 00H R

Symbol 7 6 5 4 3 2 1 0

FSASTL 0 0 0 SEQER 0 0 WRER ERER

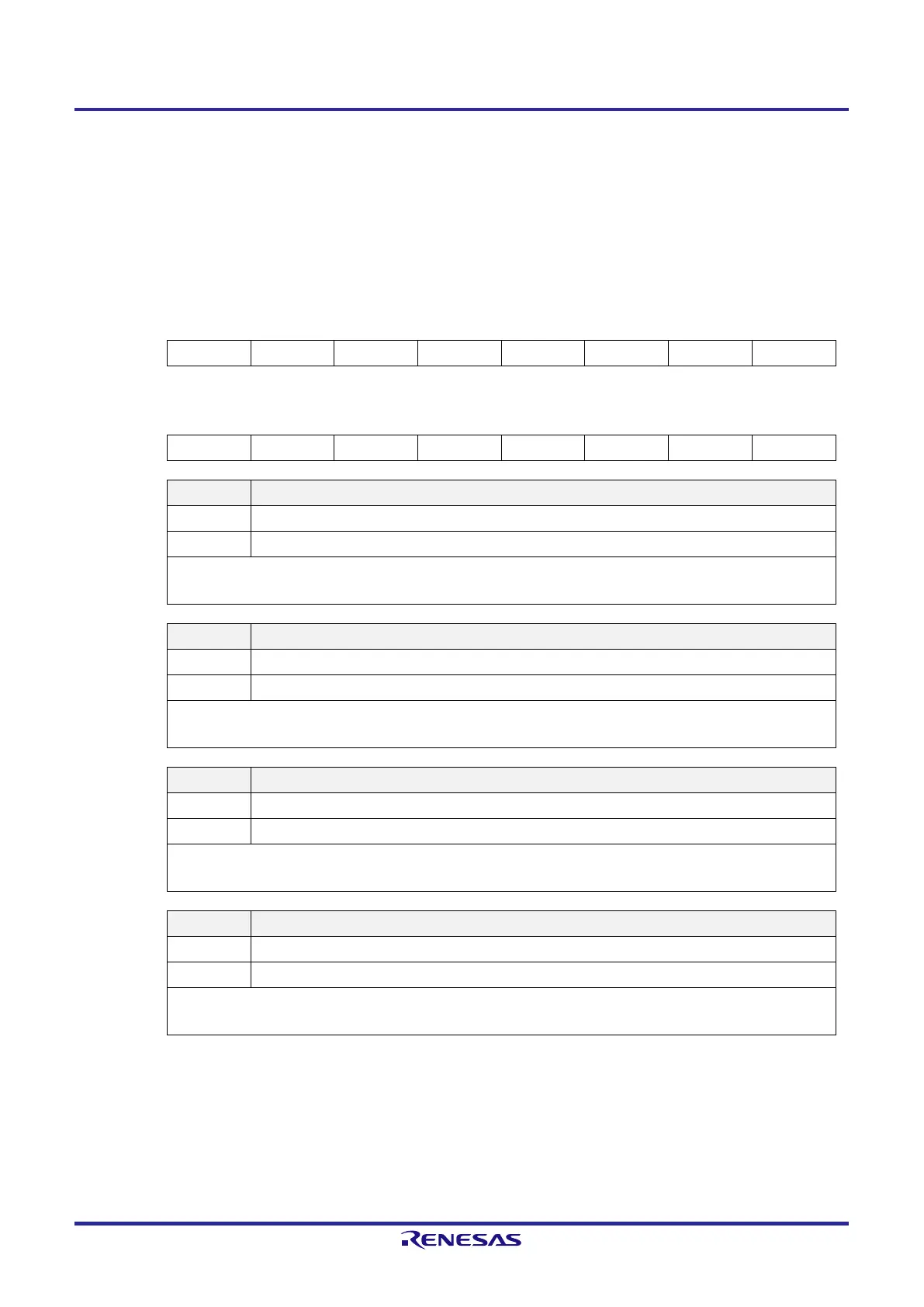

SQEND Flash memory sequencer operation status flag

0 Operation is in progress.

1 Operation has ended.

<Clearing condition>

The SQST bit being cleared.

SEQER Flash memory sequencer error flag

0 No error has occurred.

1 An error has occurred.

<Clearing condition>

Next activation of the flash memory sequencer

WRER Write command error flag

0 No error has occurred.

1 An error has occurred.

<Clearing condition>

Activation of the next command action

ERER Block erase command error flag

0 No error has occurred.

1 An error has occurred.

<Clearing condition>

Next activation of the flash memory sequencer

Loading...

Loading...