RL78/G15 CHAPTER 13 SERIAL INTERFACE IICA

R01UH0959EJ0110 Rev.1.10 Page 514 of 765

Mar 7, 2023

13.3.2 IICA control register 00 (IICCTL00)

This register is used to enable or stop I

2

C operations, set the timing of clock stretching, and set other I

2

C operations.

The IICCTL00 register can be set by a 1-bit or 8-bit memory manipulation instruction. Note that the SPIE0, WTIM0, and

ACKE0 bits must be set while the setting of IICE0 is 0 or during the clock stretch period. These bits can be set at the

same time when the IICE0 bit is set from 0 to 1.

Reset signal generation clears this register to 00H.

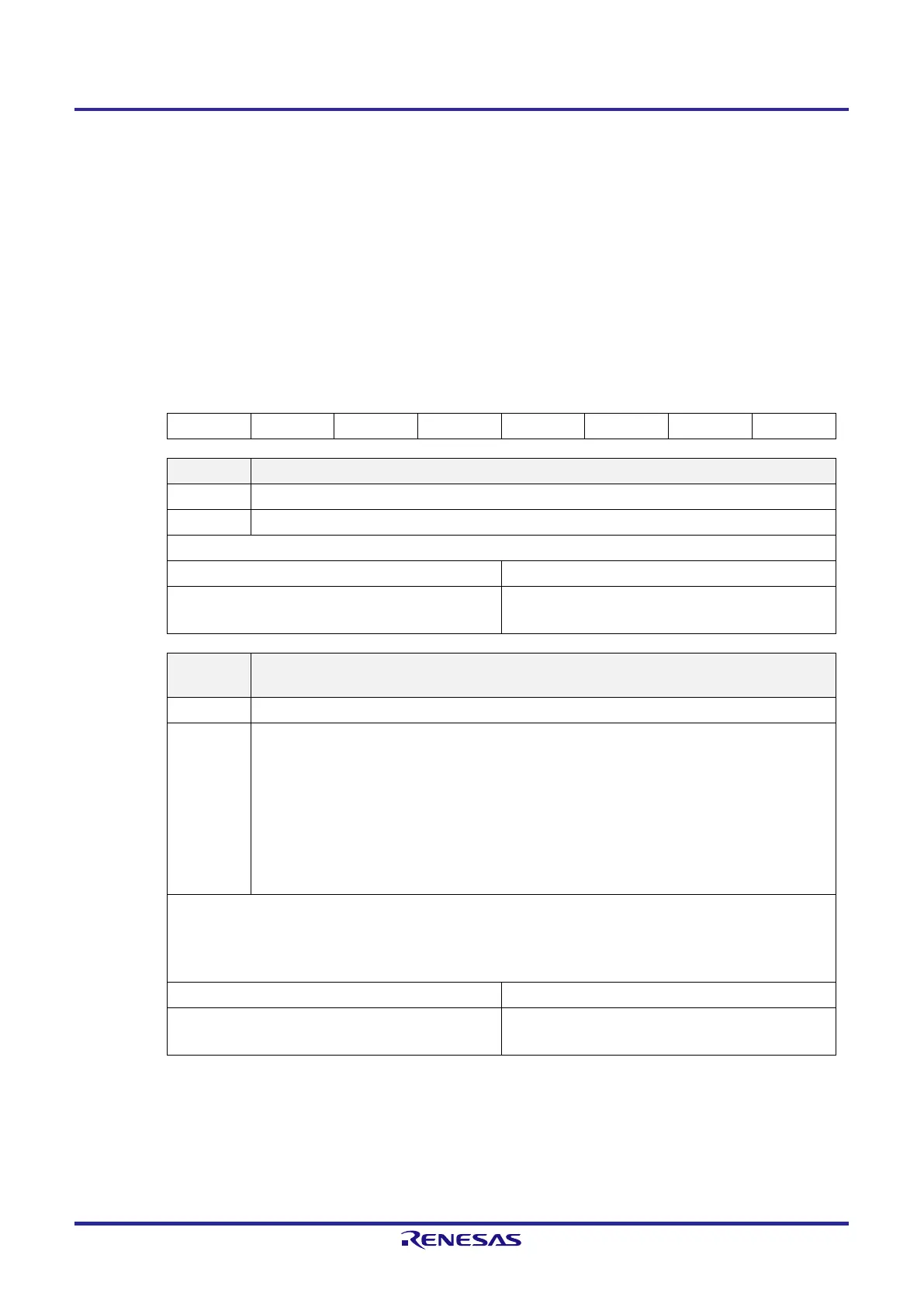

Figure 13-6. Format of IICA Control Register 00 (IICCTL00) (1/4)

Address: F0230H After reset: 00H R/W

Symbol

□

7

□

6

□

5

□

4

□

3

□

2

□

1

□

0

IICCTL00 IICE0 LREL0 WREL0 SPIE0 WTIM0 ACKE0 STT0 SPT0

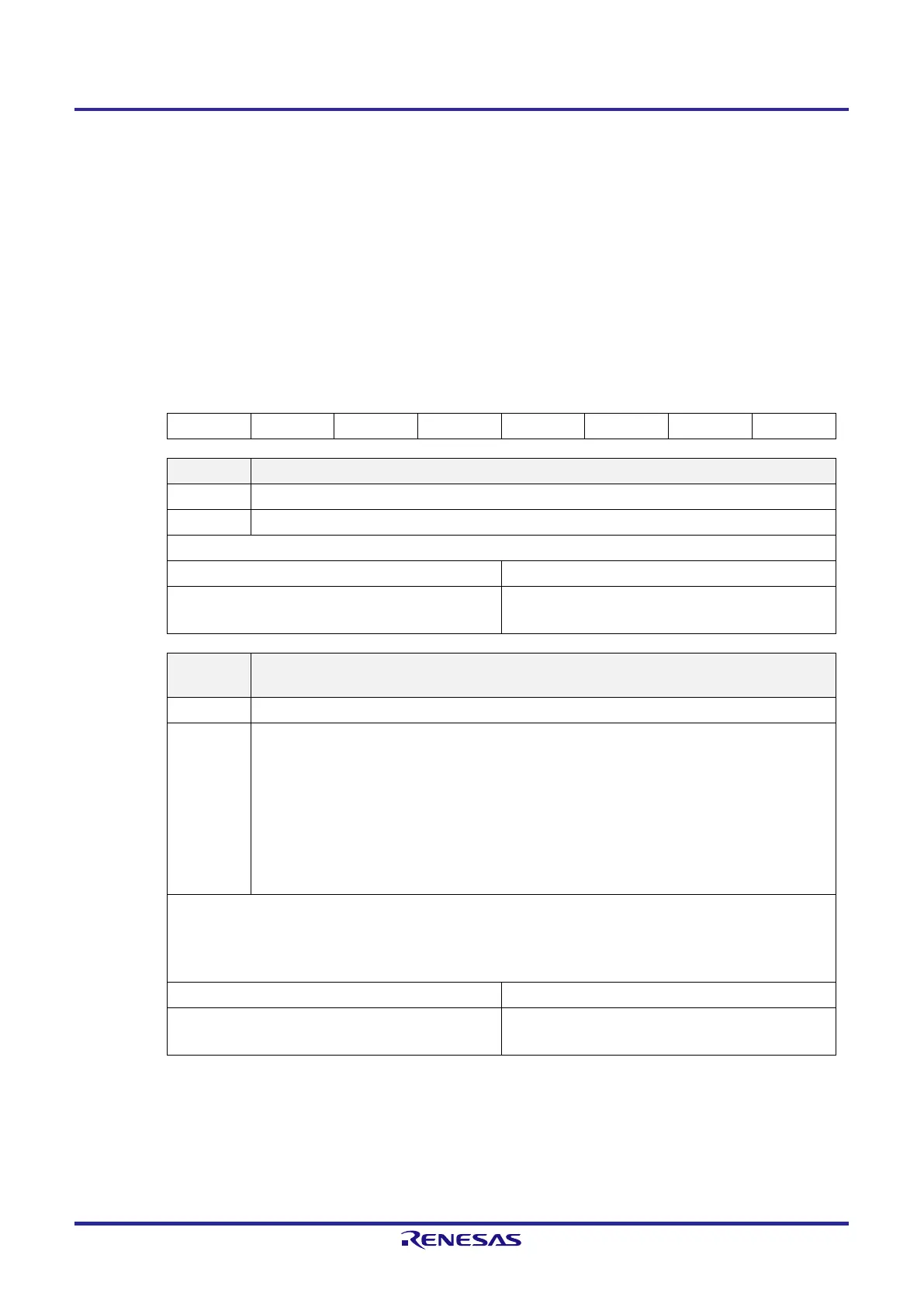

IICE0 I

2

C operation enable

0 Stops operation. Resets IICA status register 0 (IICS0)

Note 1

. Also stops internal operation.

1 Enables operation.

Be sure to set this bit (1) while the SCLA0 and SDAA0 lines are at the high level.

Condition for clearing (IICE0 = 0) Condition for setting (IICE0 = 1)

●

Cleared by instruction

●

Reset

●

Set by instruction

LREL0

Note 2, Note 3

Exit from communications

0 Normal operation

1

The device exits from the current communications and enters standby mode. This setting is

automatically cleared to 0 after having been executed.

This bit is used when an extension code not related to the local station is received.

The SCLA0 and SDAA0 lines go into the high impedance state.

The following flags of IICA control register 00 (IICCTL00) and IICA status register 0 (IICS0) are cleared

to 0.

STT0, SPT0, MSTS0, EXC0

COI0, TRC0, ACKD0, STD0

The standby mode following exit from communications remains in effect until the following communication participation

conditions are met.

●

After a stop condition is detected, startup is in master mode.

●

An address match or extension code reception after the start condition

Condition for clearing (LREL0 = 0) Condition for setting (LREL0 = 1)

●

Automatically cleared after execution

●

Reset

●

Set by instruction

Loading...

Loading...