RL78/G15 CHAPTER 13 SERIAL INTERFACE IICA

R01UH0959EJ0110 Rev.1.10 Page 537 of 765

Mar 7, 2023

13.5.6 Clock stretching

Clock stretching is used to notify the other party in communications that a master or slave is preparing to transmit or

receive data (i.e., in the clock stretch state).

By setting the SCLA0 pin to the low level, the other party is notified of the clock stretch state. When both the master and

slave are released from the clock stretch state, the next data transfer can be started.

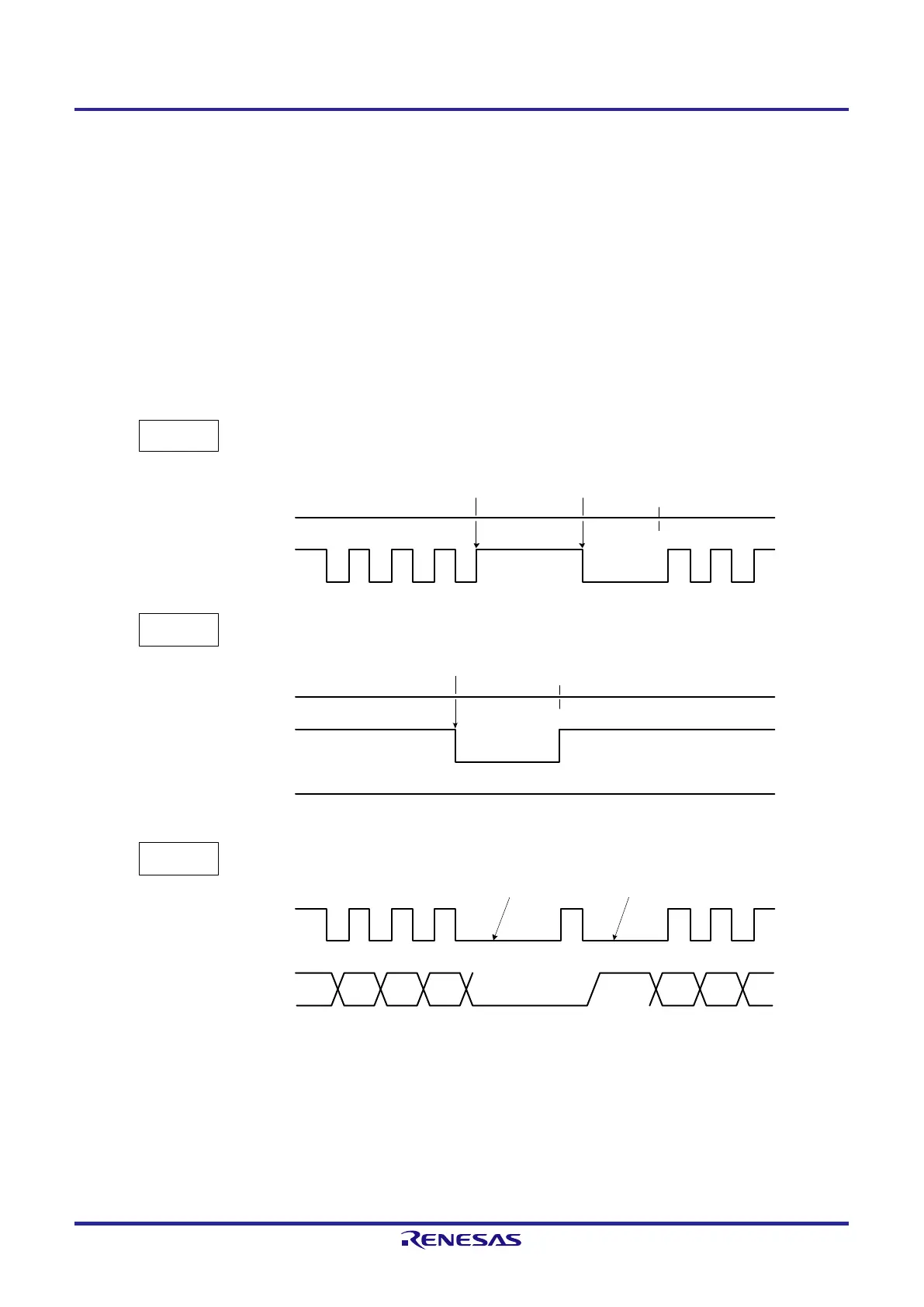

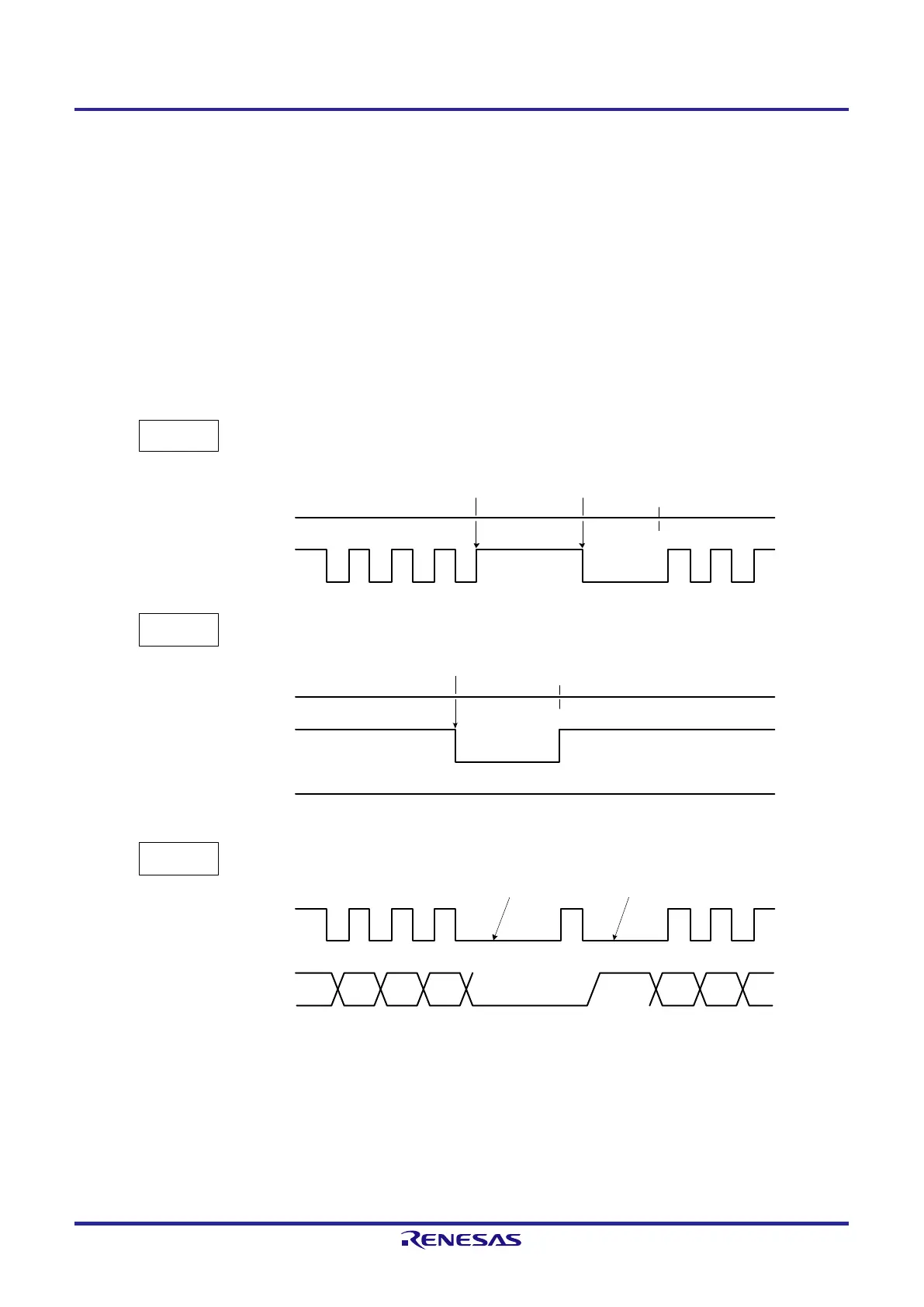

Figure 13-19. Clock Stretching (1/2)

(1) When clock stretching occurs at the falling edge of the 9th clock for the master and at the falling edge of the 8th clock

for the slave (master: transmission, slave: reception, and ACKE0 = 1)

Master

Slave

Transfer line

IICA0

SCLA0

IICA0

SCLA0

ACKE0

SCLA0

SDAA0

6 7 8 9 1 2 3

The master returns to the high

impedance state but the slave

is in the clock stretch state (at

the low level).

The clock is stretched after

the 9th clock output.

IICA0 data write

(release clock stretching)

The clock is stretched after

the 8th clock output.

Clock stretching from

the slave

Clock stretching from

the master

FFH is written to IICA0 or WREL0 is set to 1.

6 7 8 9 1 2 3

D2 D1 D0 D7 D6 D5

ACK

H

Loading...

Loading...