RL78/G15 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0959EJ0110 Rev.1.10 Page 482 of 765

Mar 7, 2023

12.6.4 Procedure for Processing Errors that Occurred During UART (UART0)

Communication

The procedure for processing errors that occurred during UART (UART0) communication is described in Figure 12-83

and Figure 12-84.

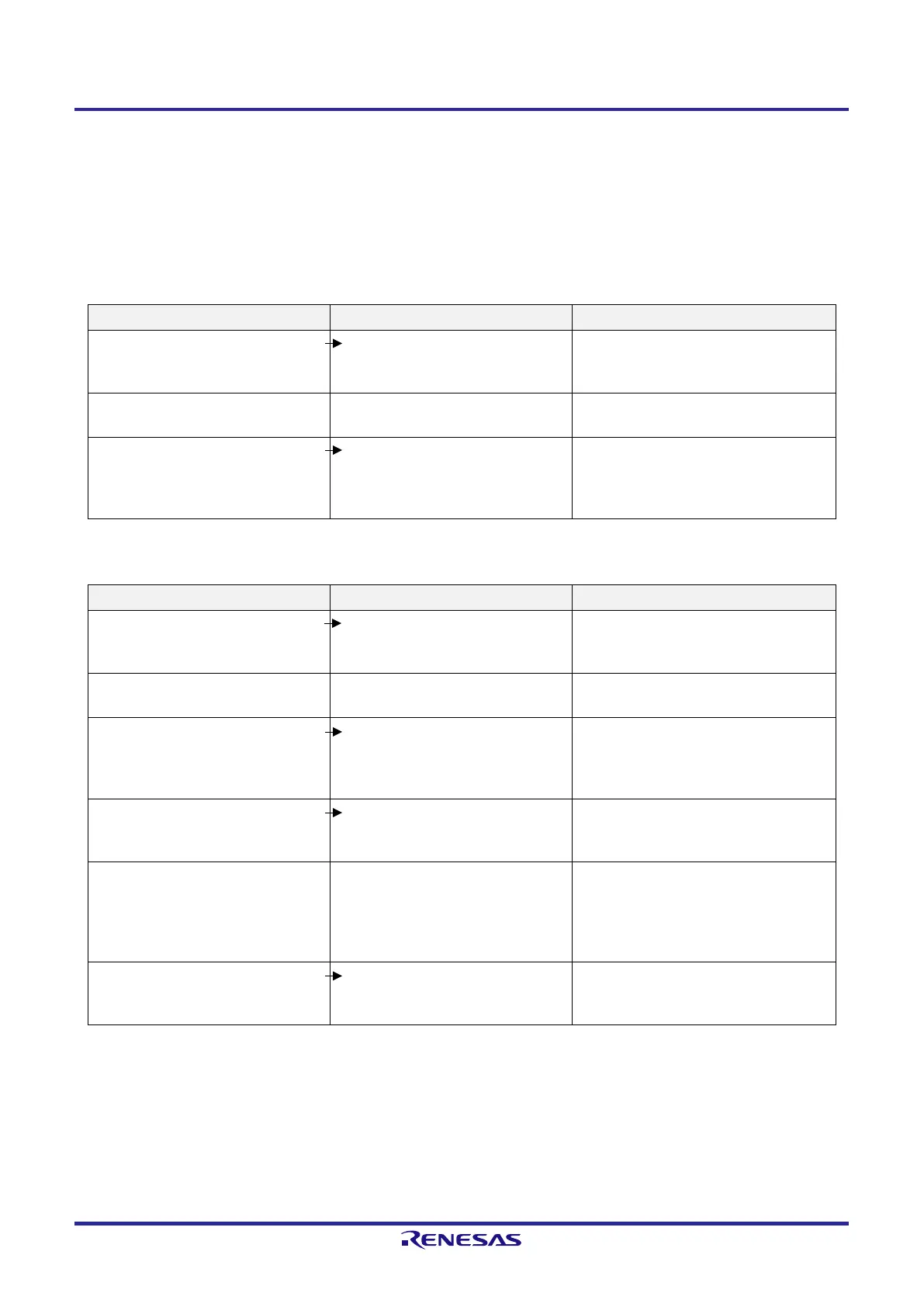

Figure 12-83. Processing Procedure in Case of Parity Error or Overrun Error

Software Manipulation State of the Hardware Remark

Reads serial data register mn (SDRmn).

The BFFmn bit of the SSRmn register

is set to 0 and channel n is enabled to

receive data.

This is to prevent an overrun error if the next

reception is completed during error

processing.

Reads serial status register mn

(SSRmn).

The error type is identified and the read value

is used to clear the error flag.

Writes 1 to serial flag clear trigger

register mn (SIRmn).

The error flag is cleared.

Only the error generated during reading can

be cleared, by writing the value read from the

SSRmn register to the SIRmn register without

modification.

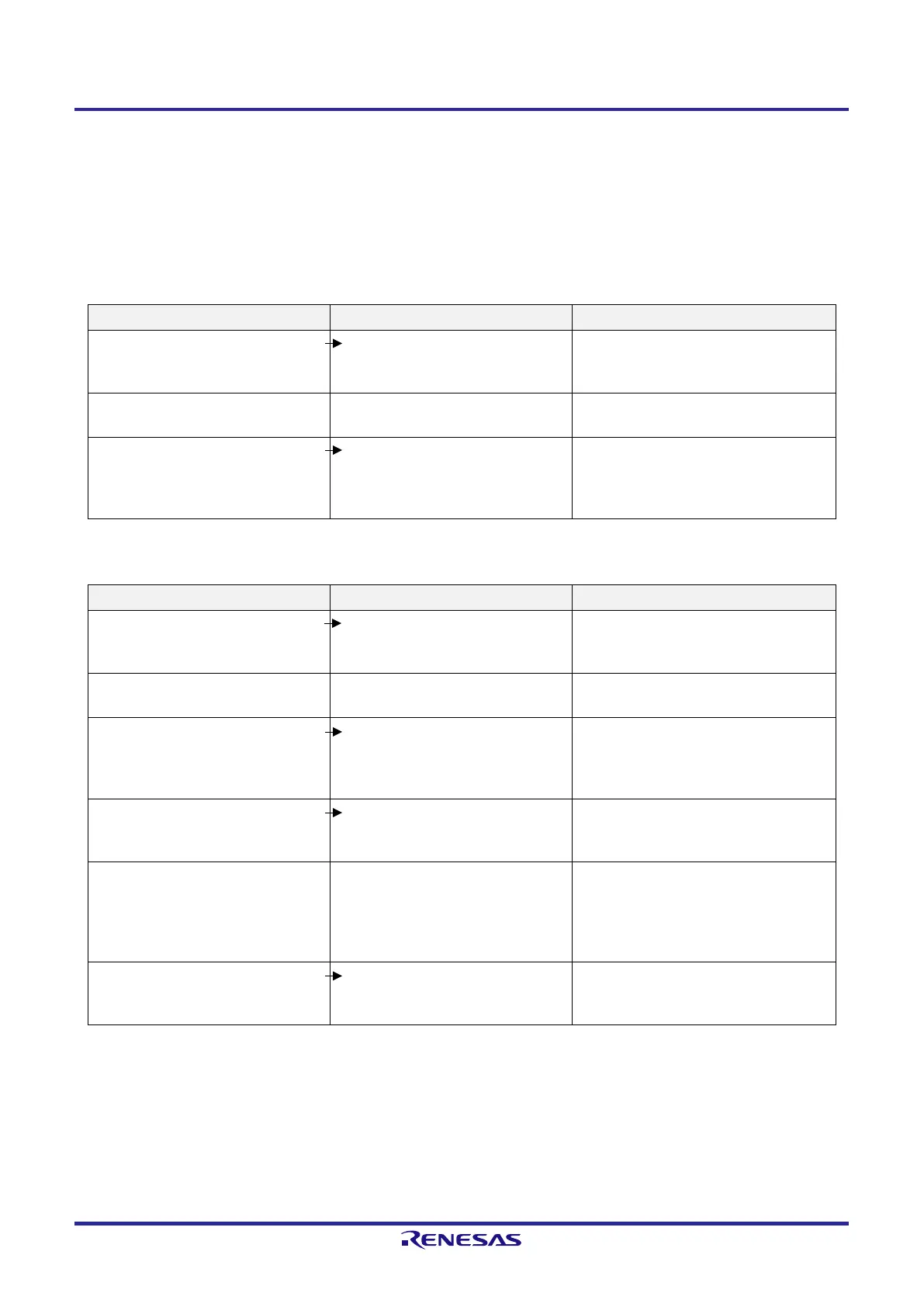

Figure 12-84. Processing Procedure in Case of Framing Error

Software Manipulation State of the Hardware Remark

Reads serial data register mn (SDRmn).

The BFFmn bit of the SSRmn register

is set to 0 and channel n is enabled to

receive data.

This is to prevent an overrun error if the next

reception is completed during error

processing.

Reads serial status register mn

(SSRmn).

The error type is identified and the read value

is used to clear the error flag.

Writes serial flag clear trigger register

mn (SIRmn).

The error flag is cleared.

Only the error generated during reading can

be cleared, by writing the value read from the

SSRmn register to the SIRmn register without

modification.

Sets the STmn bit of serial channel stop

register m (STm) to 1.

The SEmn bit of serial channel enable

status register m (SEm) is set to 0 and

channel n stops operation.

Synchronization with other party of

communication

Synchronization with the other party of

communication is re-established and

communication is resumed because it is

considered that a framing error has occurred

because the start bit has been shifted.

Sets the SSmn bit of serial channel start

register m (SSm) to 1.

The SEmn bit of serial channel enable

status register m (SEm) is set to 1 and

channel n is enabled to operate.

Remark m: Unit number (m = 0), n: Channel number (n = 1), mn = 01

Loading...

Loading...