RL78/G15 CHAPTER 4 PORT FUNCTIONS

R01UH0959EJ0110 Rev.1.10 Page 109 of 765

Mar 7, 2023

4.3.4 Port input mode registers 0, 2, 4 (POM0, POM2, POM4)

These registers set CMOS output or N-ch open drain output in 1-bit units.

N-ch open drain output (V

DD

tolerance) mode can be selected for the SDA00 and SDA01 pins during simplified I

2

C

communication with an external device.

These registers can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears these registers to 00H.

Caution An on-chip pull-up resistor is not connected to a bit for which N-ch open drain output (V

DD

tolerance)

mode (POMmn = 1) is set.

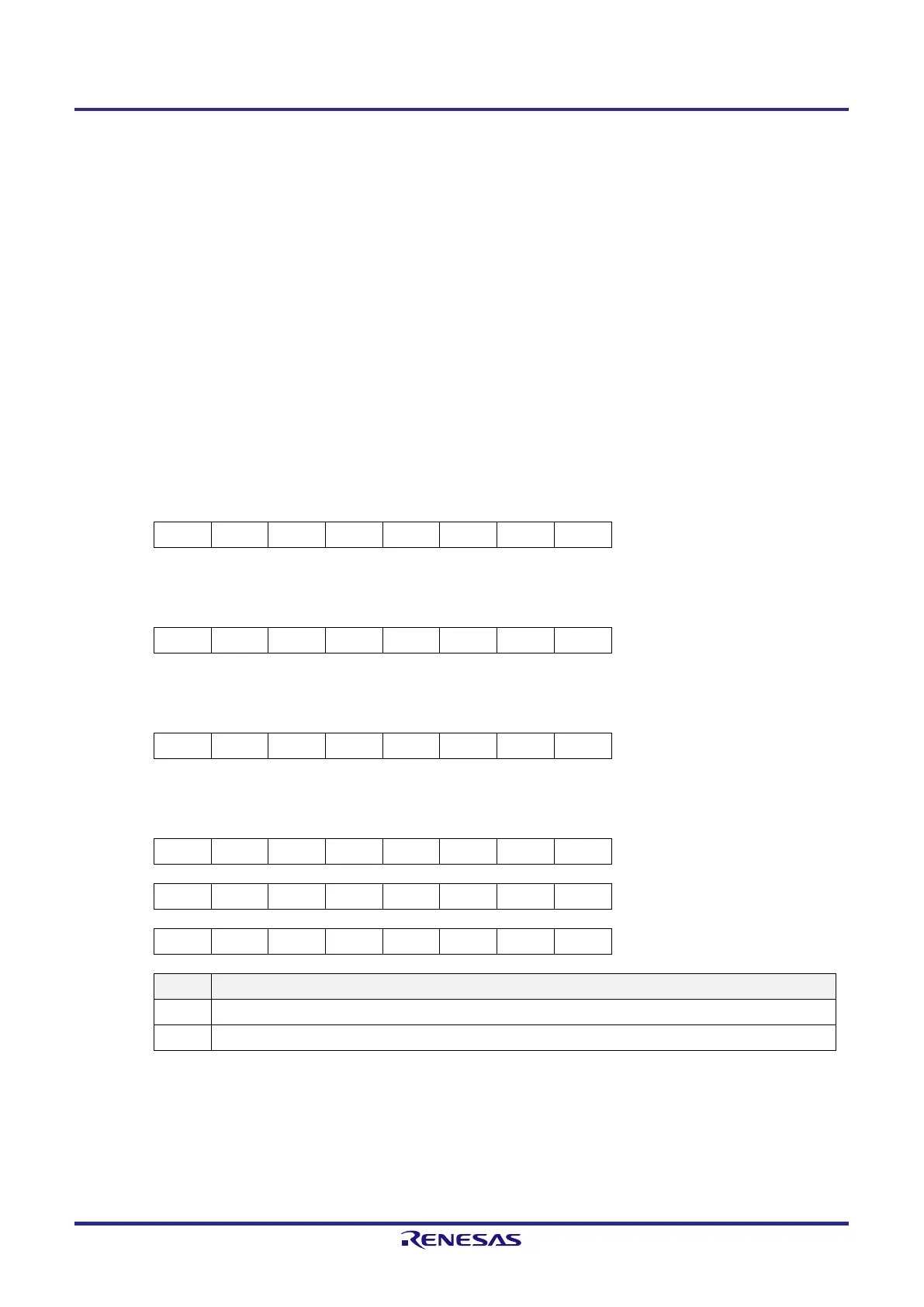

Figure 4-4. Format of Port Output Mode Registers 0, 2, 4 (POM0, POM2, POM4)

8-pin products

Symbol 7 6 5 4 3 2 1 0 Address After reset R/W

POM0 0 0 0 0 POM03 0 POM01 0 F0050H 00H R/W

10-pin products

Symbol 7 6 5 4 3 2 1 0 Address After reset R/W

POM0 0 0 0 0 POM03 0 POM01 POM00 F0050H 00H R/W

16-pin products

Symbol 7 6 5 4 3 2 1 0 Address After reset R/W

POM0 POM07 POM06 POM05 POM04 POM03 0 POM01 POM00 F0050H 00H R/W

20-pin products

Symbol 7 6 5 4 3 2 1 0 Address After reset R/W

POM0 POM07 POM06 POM05 POM04 POM03 0 POM01 POM00 F0050H 00H R/W

POM2 0 0 0 0 0 POM22 0 0 F0052H 00H R/W

POM4 0 0 0 0 0 0 POM41 0 F0054H 00H R/W

POMmn P0n pin output mode selection

0 Normal output mode

1 N-ch open-drain output (V

DD

tolerance) mode

Remark m = 0, 2, 4

n = 0 to 7

Caution Be sure to set bits that are not mounted to their initial values.

Loading...

Loading...