RL78/G15 CHAPTER 11 COMPARATOR

R01UH0959EJ0110 Rev.1.10 Page 353 of 765

Mar 7, 2023

11.3.3 Comparator Filter Control Register (COMPFIR)

This register selects the effective edge for the comparator interrupt signal, and enables or disables the digital filter.

If noise elimination is required, set the CnFCK1 and CnFCK0 bits (n = 1, 0) so that the digital filter is enabled. When the

digital filter is enabled, the comparator output is checked if its level remains the same for three consecutive digital filter

sampling clock cycles.

The COMPFIR register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

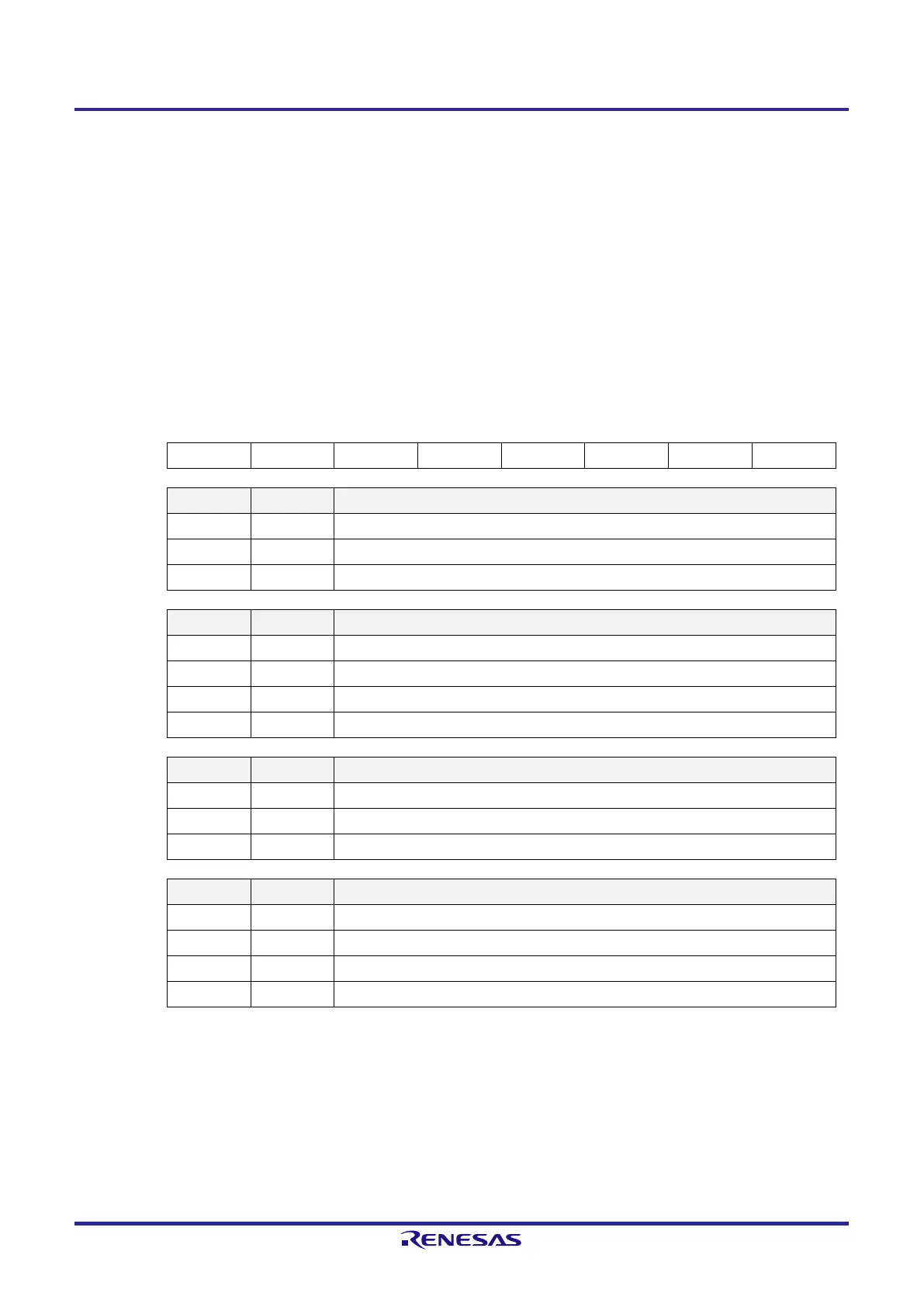

Figure 11-4. Format of Comparator Filter Control Register (COMPFIR)

Address: FFF61H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

COMPFIR C1EDG C1EPO C1FCK1 C1FCK0 C0EDG C0EPO C0FCK1 C0FCK0

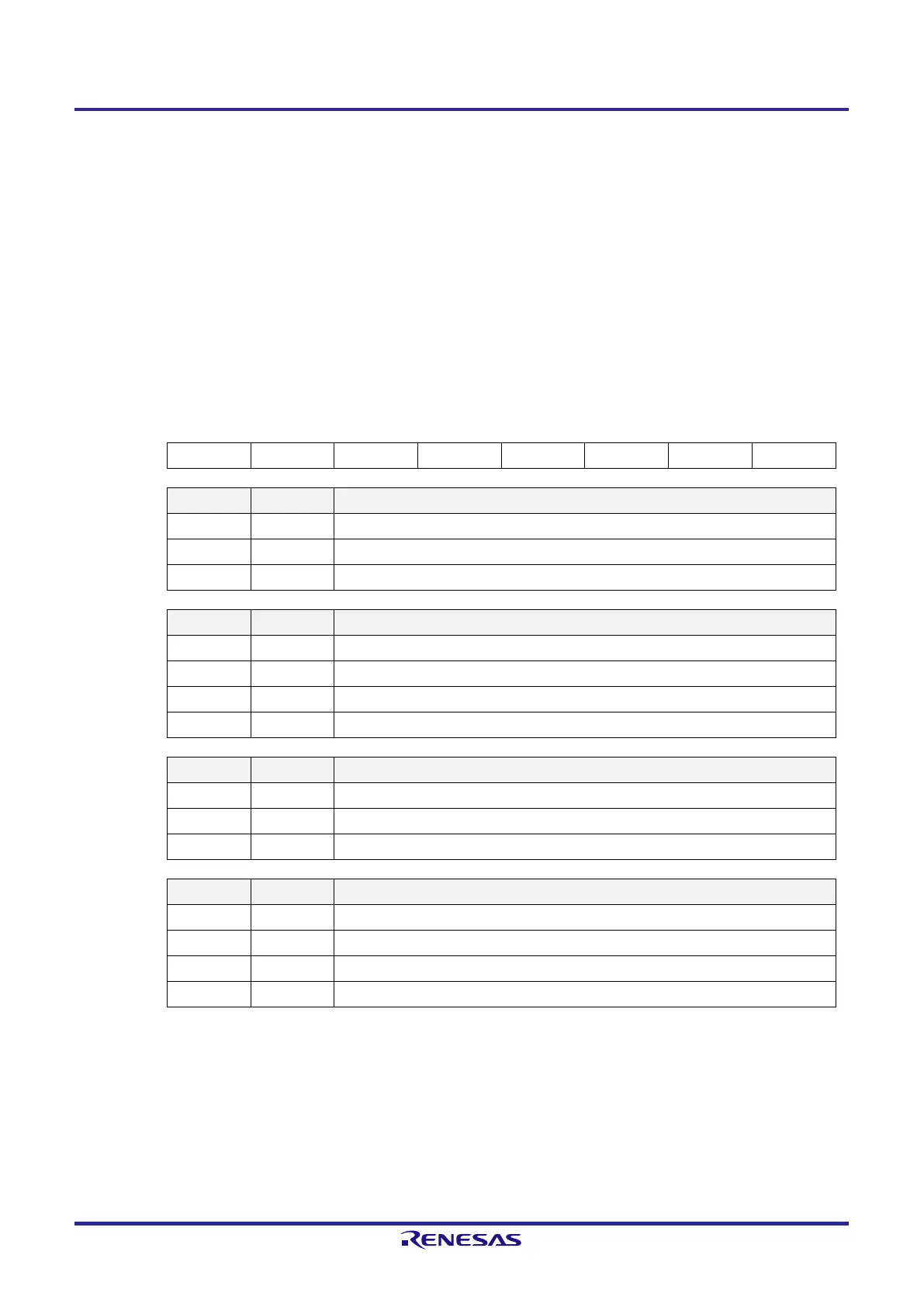

C1EDG C1EPO Effective edge selection for comparator 1 interrupt signal

Note 1

0 0 Rising edge

0 1 Falling edge

1 × Both rising and falling edges

C1FCK1 C1FCK0 Comparator 1 digital filter enable/disable

Note 1, Note 2, Note 3

0 0 Digital filter disabled

0 1 Digital filter enabled, sampling clock: f

CLK

1 0 Digital filter enabled, sampling clock: f

CLK

/8

1 1 Digital filter enabled, sampling clock: f

CLK

/32

C0EDG C0EPO Effective edge selection for comparator 0 interrupt signal

Note 4

0 0 Rising edge

0 1 Falling edge

1 × Both rising and falling edges

C0FCK1 C0FCK0 Comparator 0 digital filter enable/disable

Note 4, Note 5, Note 6

0 0 Digital filter disabled

0 1 Digital filter enabled, sampling clock: f

CLK

1 0 Digital filter enabled, sampling clock: f

CLK

/8

1 1 Digital filter enabled, sampling clock: f

CLK

/32

Note 1. If the C1EDG, C1EPO, and C1FCK1 or C1FCK0 bits are changed while operation of the comparator 1 is

enabled, a comparator detection 1 interrupt (INTCMP1) may be generated. Change these bits only after

clearing the C1IE bit in the COMPOCR register to 0 to disable an interrupt request.

Also, be sure to clear bit 2 (CMPIF1) in the interrupt request flag register 1H (IF1H) to 0 after changing these

bits.

Note 2. If the value of the C1FCK1 or C1FCK0 bit is changed, a wait period of four cycles of the sampling clock is

required to update the digital filter. To use the comparator detection 1 interrupt (INTCMP1), set the C1IE bit in

the COMPOCR register to 1 after this wait period.

Loading...

Loading...