RL78/G15 CHAPTER 22 INSTRUCTION SET

R01UH0959EJ0110 Rev.1.10 Page 706 of 765

Mar 7, 2023

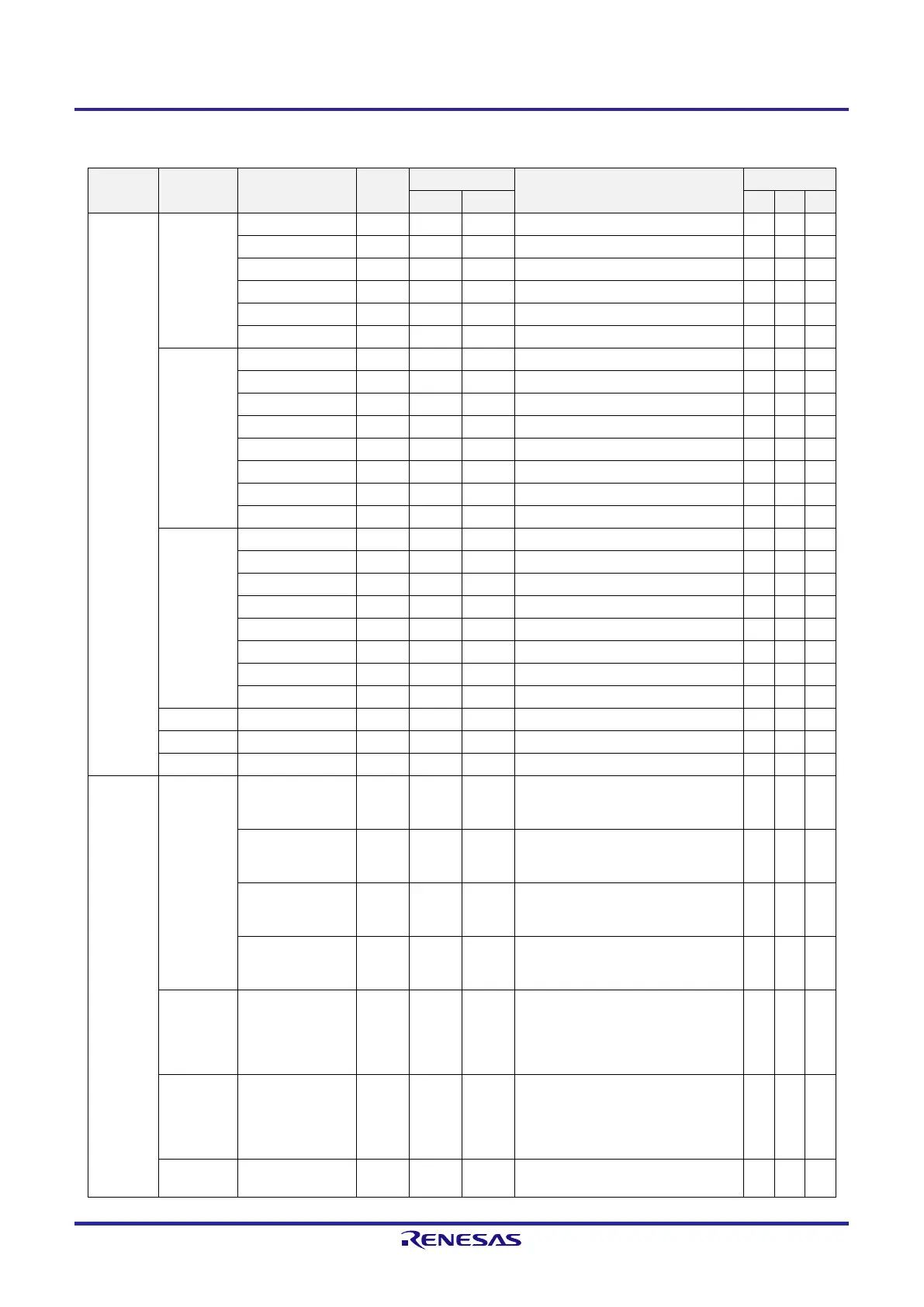

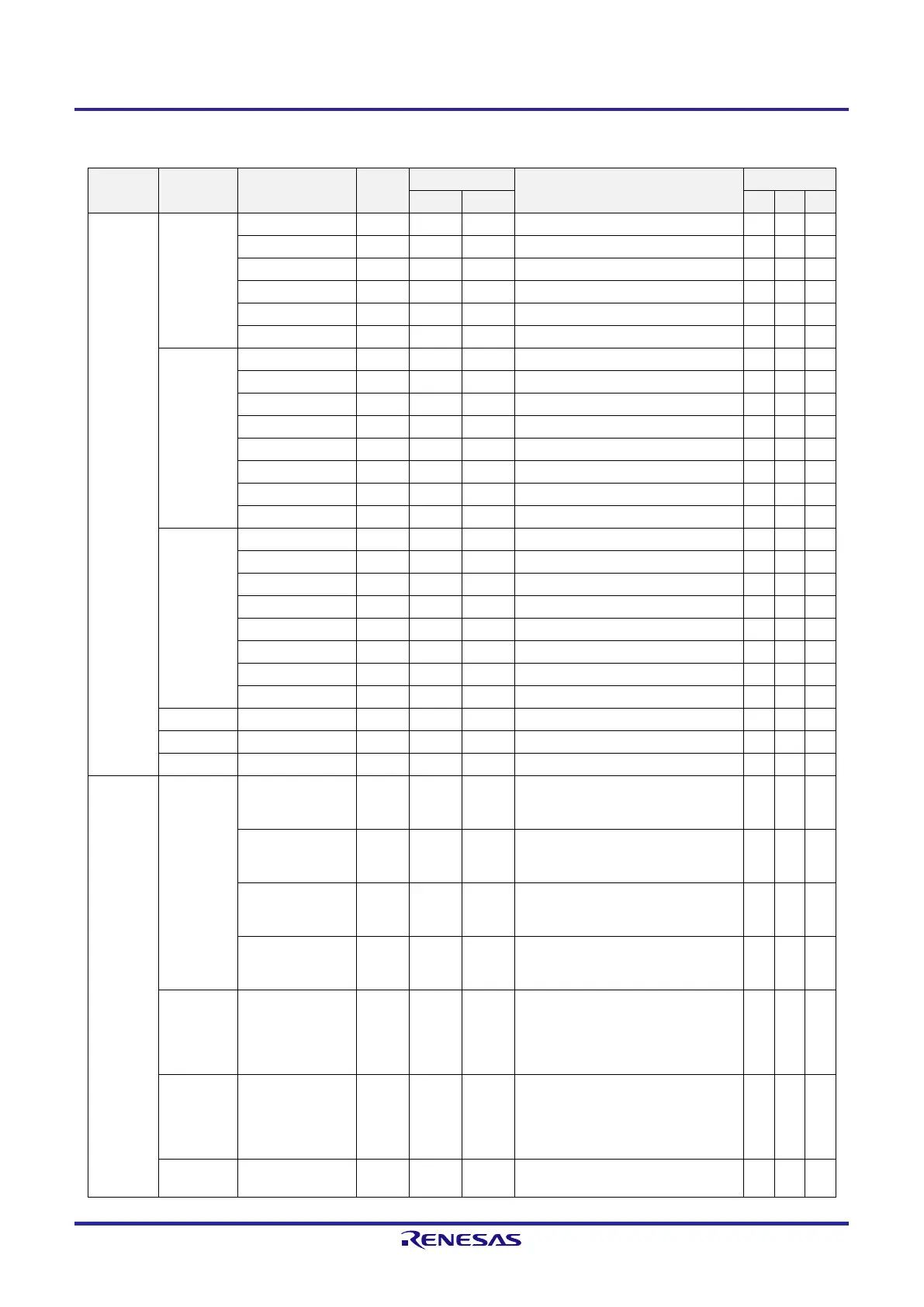

Table 22-5. Operation List (11/13)

Instruction

Group

Mnemonic Operand Bytes Clock Operation Flag

Note 1 Note 2

Z AC CY

Bit

manipulate

XOR1 CY, A.bit 2 1 — CY ← CY ∀ A.bit ×

CY, PSW.bit 3 1 — CY ← CY ∀ PSW.bit ×

CY, saddr.bit 3 1 — CY ← CY ∀ (saddr).bit ×

CY, sfr.bit 3 1 — CY ← CY ∀ sfr.bit ×

CY, [HL].bit 2 1 4 CY ← CY ∀ (HL).bit ×

CY, ES:[HL].bit 3 2 5 CY ← CY ∀ (ES, HL).bit ×

SET1 A.bit 2 1 — A.bit ← 1

PSW.bit 3 4 — PSW.bit ← 1 × × ×

!addr16.bit 4 2 — (addr16).bit ← 1

ES:!addr16.bit 5 3 — (ES, addr16).bit ← 1

saddr.bit 3 2 — (saddr).bit ← 1

sfr.bit 3 2 — sfr.bit ← 1

[HL].bit 2 2 — (HL).bit ← 1

ES:[HL].bit 3 3 — (ES, HL).bit ← 1

CLR1 A.bit 2 1 — A.bit ← 0

PSW.bit 3 4 — PSW.bit ← 0 × × ×

!addr16.bit 4 2 — (addr16).bit ← 0

ES:!addr16.bit 5 3 — (ES, addr16).bit ← 0

saddr.bit 3 2 — (saddr).bit ← 0

sfr.bit 3 2 — sfr.bit ← 0

[HL].bit 2 2 — (HL).bit ← 0

ES:[HL].bit 3 3 — (ES, HL).bit ← 0

SET1 CY 2 1 — CY ← 1 1

CLR1 CY 2 1 — CY ← 0 0

NOT1 CY 2 1 — CY ← CY

¯¯

×

Call/return CALL rp 2 3 — (SP − 2) ← (PC + 2)

S

, (SP − 3) ← (PC + 2)

H

,

(SP − 4) ← (PC + 2)

L

, PC ← CS, rp,

SP ← SP − 4

$!addr20 3 3 — (SP − 2) ← (PC + 3)

S

, (SP − 3) ← (PC + 3)

H

,

(SP − 4) ← (PC + 3)

L

, PC ← PC + 3 +

jdisp16, SP ← SP − 4

!addr16 3 3 — (SP − 2) ← (PC + 3)

S

, (SP − 3) ← (PC + 3)

H

,

(SP − 4) ← (PC + 3)

L

, PC ← 0000, addr16,

SP ← SP − 4

!!addr20 4 3 — (SP − 2) ← (PC + 4)

S

, (SP − 3) ← (PC + 4)

H

,

(SP − 4) ← (PC + 4)

L

, PC ← addr20,

SP ← SP − 4

CALLT [addr5] 2 5 — (SP − 2) ← (PC + 2)

S

, (SP − 3) ← (PC + 2)

H

,

(SP − 4) ← (PC + 2)

L

, PCS ← 0000,

PC

H

← (0000, addr5 + 1),

PC

L

← (0000, addr5),

SP ← SP − 4

BRK — 2 5 — (SP − 1) ← PSW, (SP − 2) ← (PC + 2)

S

,

(SP − 3) ← (PC + 2)

H

, (SP − 4) ← (PC + 2)

L

,

PC

S

← 0000,

PC

H

← (0007FH), PC

L

← (0007EH),

SP ← SP − 4, IE ← 0

RET — 1 6 — PC

L

← (SP), PC

H

← (SP + 1),

PC

S

← (SP + 2), SP ← SP + 4

Loading...

Loading...