Device Overview MC9S12G-Family

MC9S12G Family Reference Manual Rev.1.27

122 NXP Semiconductors

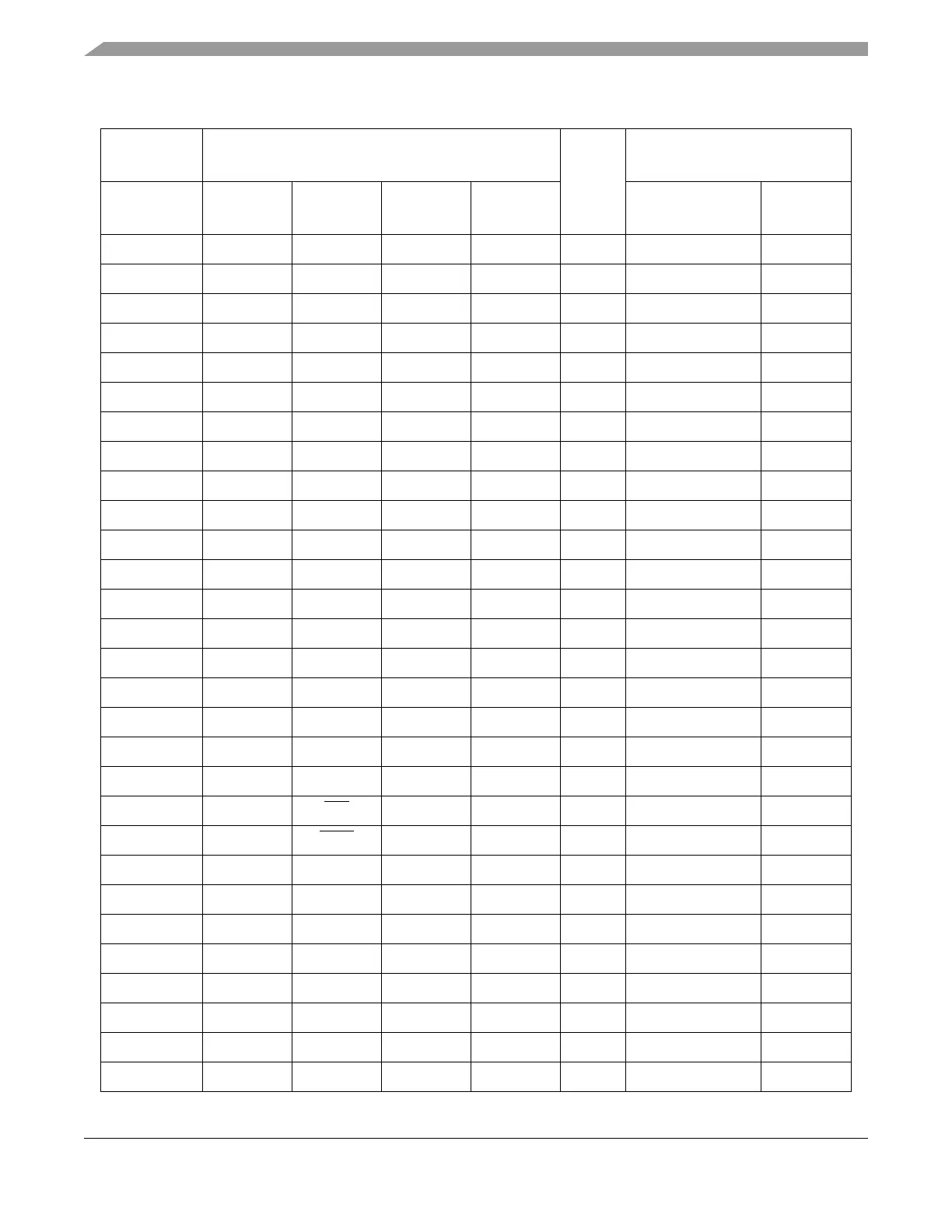

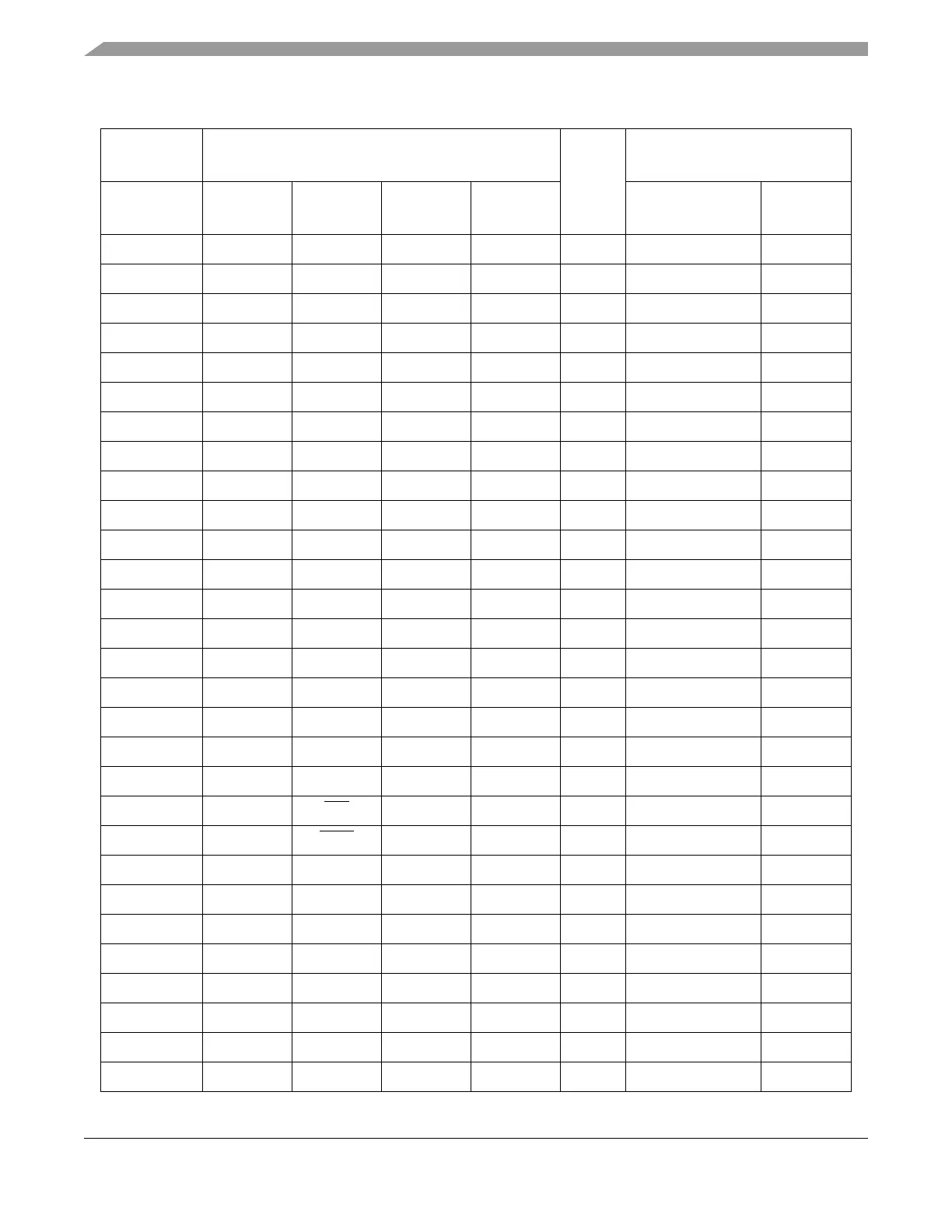

28 PB3 — — — V

DDX

PUCR/PUPBE Disabled

29 PP0 KWP0 ETRIG0 PWM0 V

DDX

PERP/PPSP Disabled

30 PP1 KWP1 ETRIG1 PWM1 V

DDX

PERP/PPSP Disabled

31 PP2 KWP2 ETRIG2 PWM2 V

DDX

PERP/PPSP Disabled

32 PP3 KWP3 ETRIG3 PWM3 V

DDX

PERP/PPSP Disabled

33 PP4 KWP4 PWM4 — V

DDX

PERP/PPSP Disabled

34 PP5 KWP5 PWM5 — V

DDX

PERP/PPSP Disabled

35 PP6 KWP6 PWM6 — V

DDX

PERP/PPSP Disabled

36 PP7 KWP7 PWM7 — V

DDX

PERP/PPSP Disabled

37 VDDX3 — — — — — —

38 VSSX3 — — — — — —

39 PT7 IOC7 — — V

DDX

PERT/PPST Disabled

40 PT6 IOC6 — — V

DDX

PERT/PPST Disabled

41 PT5 IOC5 — — V

DDX

PERT/PPST Disabled

42 PT4 IOC4 — — V

DDX

PERT/PPST Disabled

43 PT3 IOC3 — — V

DDX

PERT/PPST Disabled

44 PT2 IOC2 — — V

DDX

PERT/PPST Disabled

45 PT1 IOC1 — — V

DDX

PERT/PPST Disabled

46 PT0 IOC0 — — V

DDX

PERT/PPST Disabled

47 PB4 IRQ

——V

DDX

PUCR/PUPBE Disabled

48 PB5 XIRQ

——V

DDX

PUCR/PUPBE Disabled

49 PB6 — — — V

DDX

PUCR/PUPBE Disabled

50 PB7 — — — V

DDX

PUCR/PUPBE Disabled

51PC0———V

DDA

PUCR/PUPCE Disabled

52PC1———V

DDA

PUCR/PUPCE Disabled

53PC2———V

DDA

PUCR/PUPCE Disabled

54PC3———V

DDA

PUCR/PUPCE Disabled

55 PAD0 KWAD0 AN0 — V

DDA

PER1AD/PPS1AD Disabled

56 PAD8 KWAD8 AN8 — V

DDA

PER0AD/PPS0AD Disabled

Table 1-28. 100-Pin LQFP Pinout for S12G192 and S12G240

Function

<----lowest-----PRIORITY-----highest---->

Power

Supply

Internal Pull

Resistor

Package Pin Pin

2nd

Func.

3rd

Func.

4th

Func.

CTRL

Reset

State

Loading...

Loading...