MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 353

Chapter 10

S12 Clock, Reset and Power Management Unit (S12CPMU)

Revision History

10.1 Introduction

This specification describes the function of the Clock, Reset and Power Management Unit (S12CPMU).

• The Pierce oscillator (XOSCLCP) provides a robust, low-noise and low-power external clock

source. It is designed for optimal start-up margin with typical quartz crystals and ceramic

resonators.

• The Voltage regulator (IVREG) operates from the range 3.13V to 5.5V. It provides all the required

chip internal voltages and voltage monitors.

• The Phase Locked Loop (PLL) provides a highly accurate frequency multiplier with internal filter.

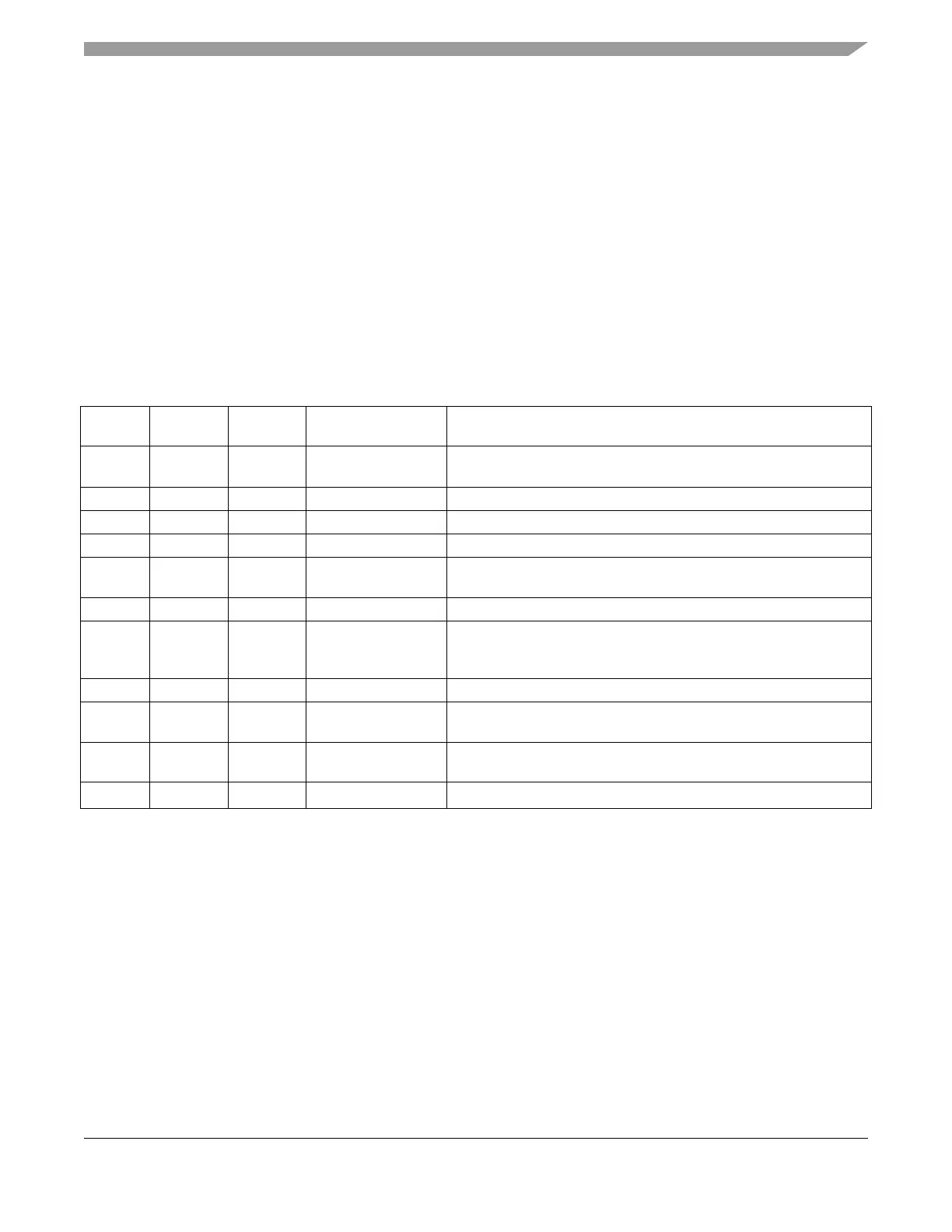

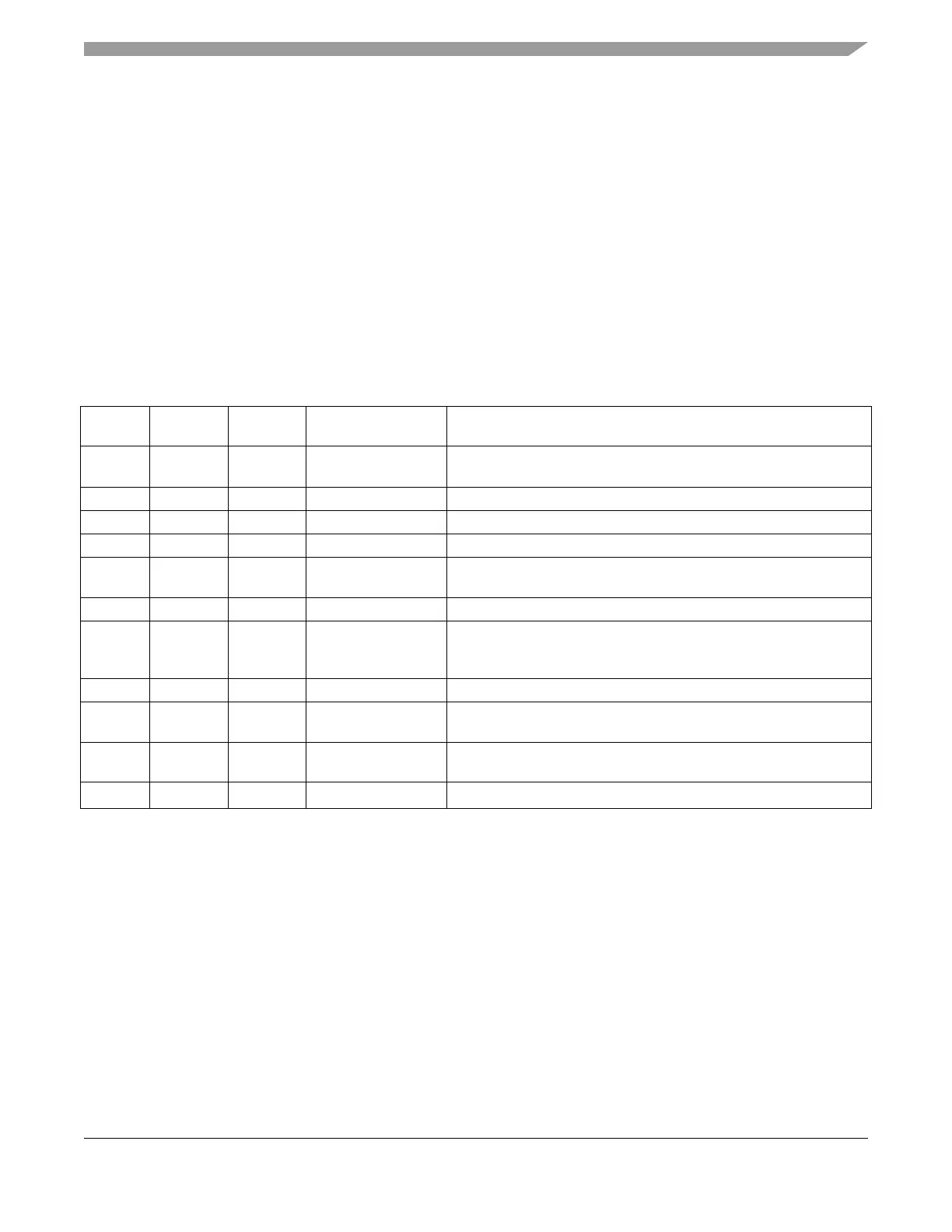

Version

Number

Revision

Date

Effective

Date

Author Description of Changes

V04.03 29 Jan 10 29 Jan 10

Added Note in section 10.3.2.16/10-380 to precise description of

API behavior after feature enable for the first time-out period.

V04.04 03 Mar 10 03 Mar 10 Corrected typos.

V04.05 23. Mar 10 23 Mar 10 Corrected typos.

V04.06 13 Apr 10 13 Apr 10 Corrected typo in Ta ble 10-6

V04.07 28 Apr 10 28 Apr 10

Major rework fixing typos, figures and tables and improved

description of Adaptive Oscillator Filter.

V04.08 03 May 10 03 Mail 10 Improved pin description in Section 10.2, “Signal Description

V04.09 22 Jun 10 22 Jun 10

Changed IP-Name from OSCLCP to XOSCLCP, added

OSCCLK_LCP clock name intoFigure 10-1 and Figure 10-2

updated description of Section 10.2.2, “EXTAL and XTAL.

V04.10 01 Jul 10 01 Jul 10 Added TC trimming to feature list

V04.11 23 Aug 10 23 Aug 10

Removed feature of adaptive oscillator filter. Register bits 6 and 4to

0in the CPMUOSC register are marked reserved and do not alter.

V04.12 27 April 12 27 April 12

Corrected wording for API interrupt flag

Changed notation of IRC trim values for 0x00000 to 0b00000

V04.13 6 Mar 13 6 Mar 13

Table 10-19. correction: substituted f

ACLK

by ACLK Clock Period

Loading...

Loading...