Device Overview MC9S12G-Family

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 141

1.10.1 Chip Configuration Summary

The different modes and the security state of the MCU affect the debug features (enabled or disabled).

The operating mode out of reset is determined by the state of the MODC signal during reset (see

Table 1-33). The MODC bit in the MODE register shows the current operating mode and provides limited

mode switching during operation. The state of the MODC signal is latched into this bit on the rising edge

of RESET.

1.10.1.1 Normal Single-Chip Mode

This mode is intended for normal device operation. The opcode from the on-chip memory is being

executed after reset (requires the reset vector to be programmed correctly). The processor program is

executed from internal memory.

1.10.1.2 Special Single-Chip Mode

This mode is used for debugging single-chip operation, boot-strapping, or security related operations. The

background debug module BDM is active in this mode. The CPU executes a monitor program located in

an on-chip ROM. BDM firmware waits for additional serial commands through the BKGD pin.

1.10.2 Low Power Operation

The MC9S12G has two static low-power modes Pseudo Stop and Stop Mode. For a detailed description

refer to S12CPMU section.

1.11 Security

The MCU security mechanism prevents unauthorized access to the Flash memory. Refer to Chapter 9,

“Security (S12XS9SECV2)”, Section 7.4.1, “Security”, and Section 29.5, “Security”.

1.12 Resets and Interrupts

Consult the S12 CPU manual and the S12SINT section for information on exception processing.

1.12.1 Resets

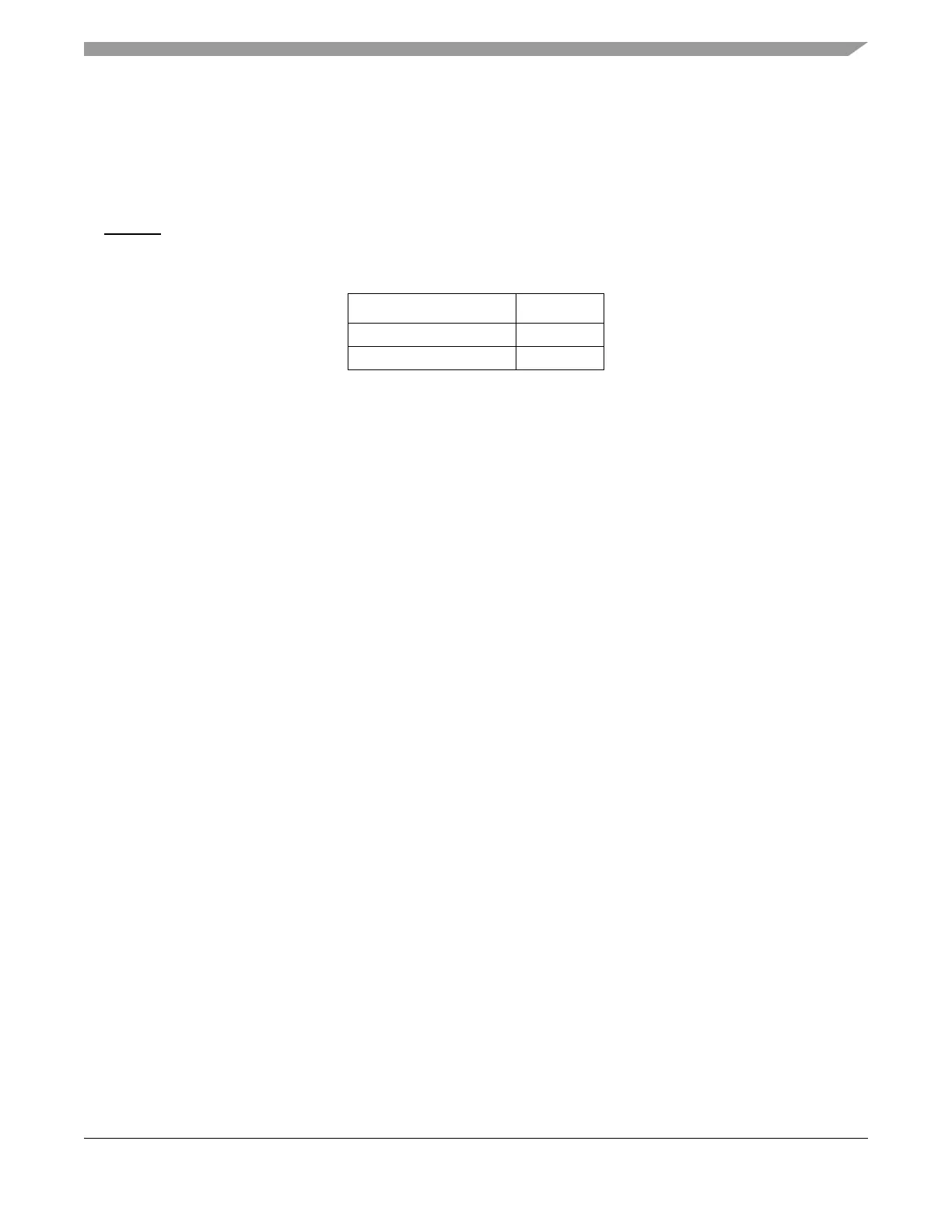

Table 1-34. lists all Reset sources and the vector locations. Resets are explained in detail in the Chapter 10,

“S12 Clock, Reset and Power Management Unit (S12CPMU)”.

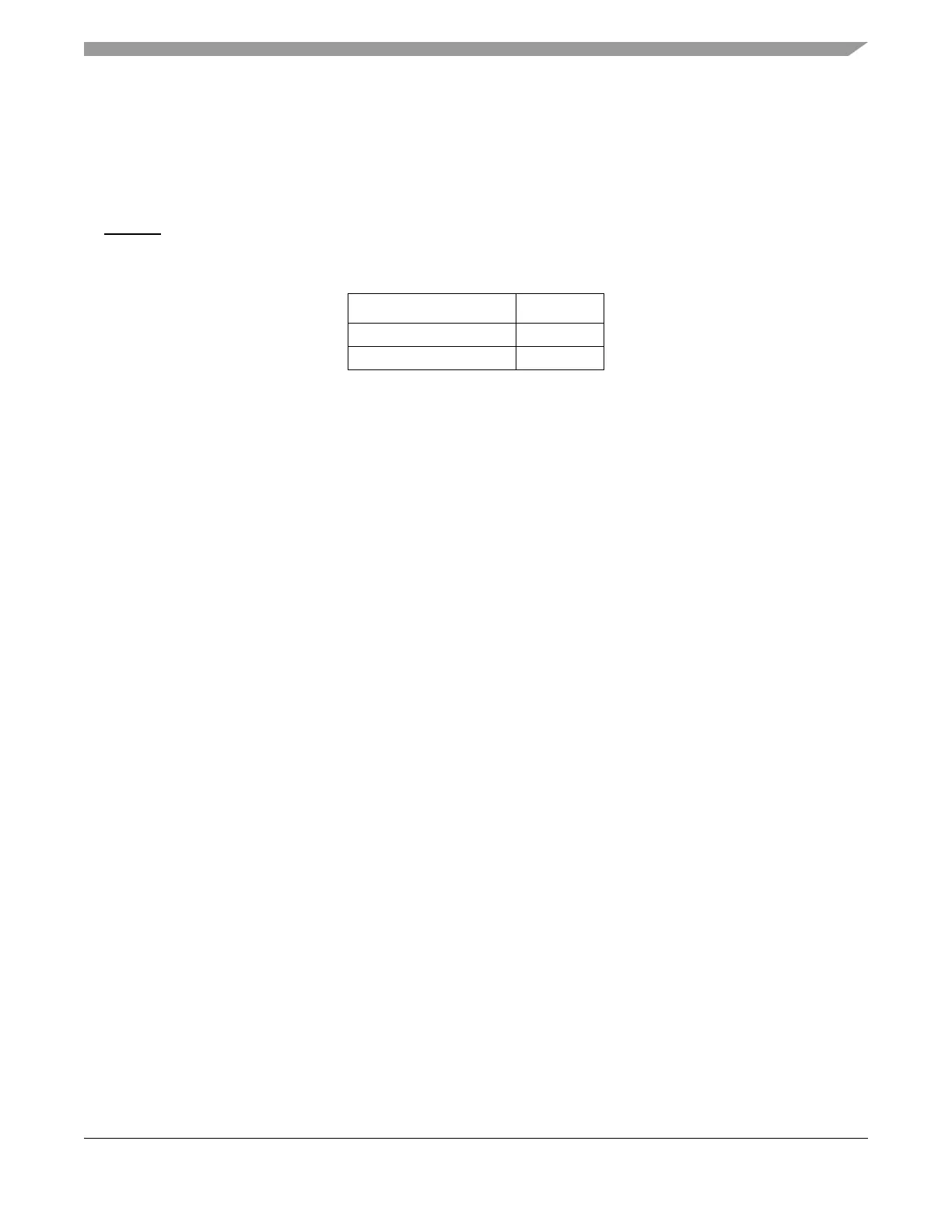

Table 1-33. Chip Modes

Chip Modes MODC

Normal single chip 1

Special single chip 0

Loading...

Loading...