Device Overview MC9S12G-Family

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 39

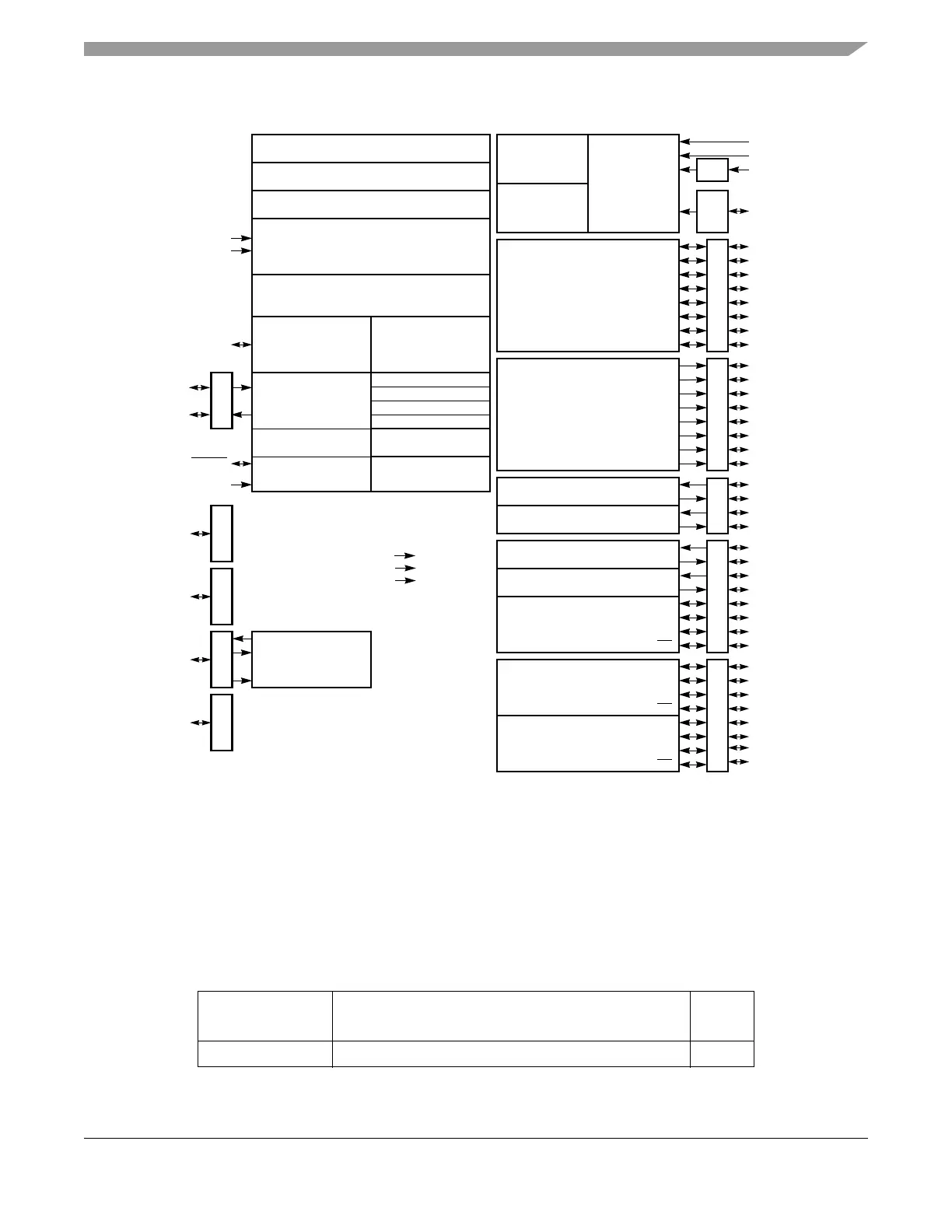

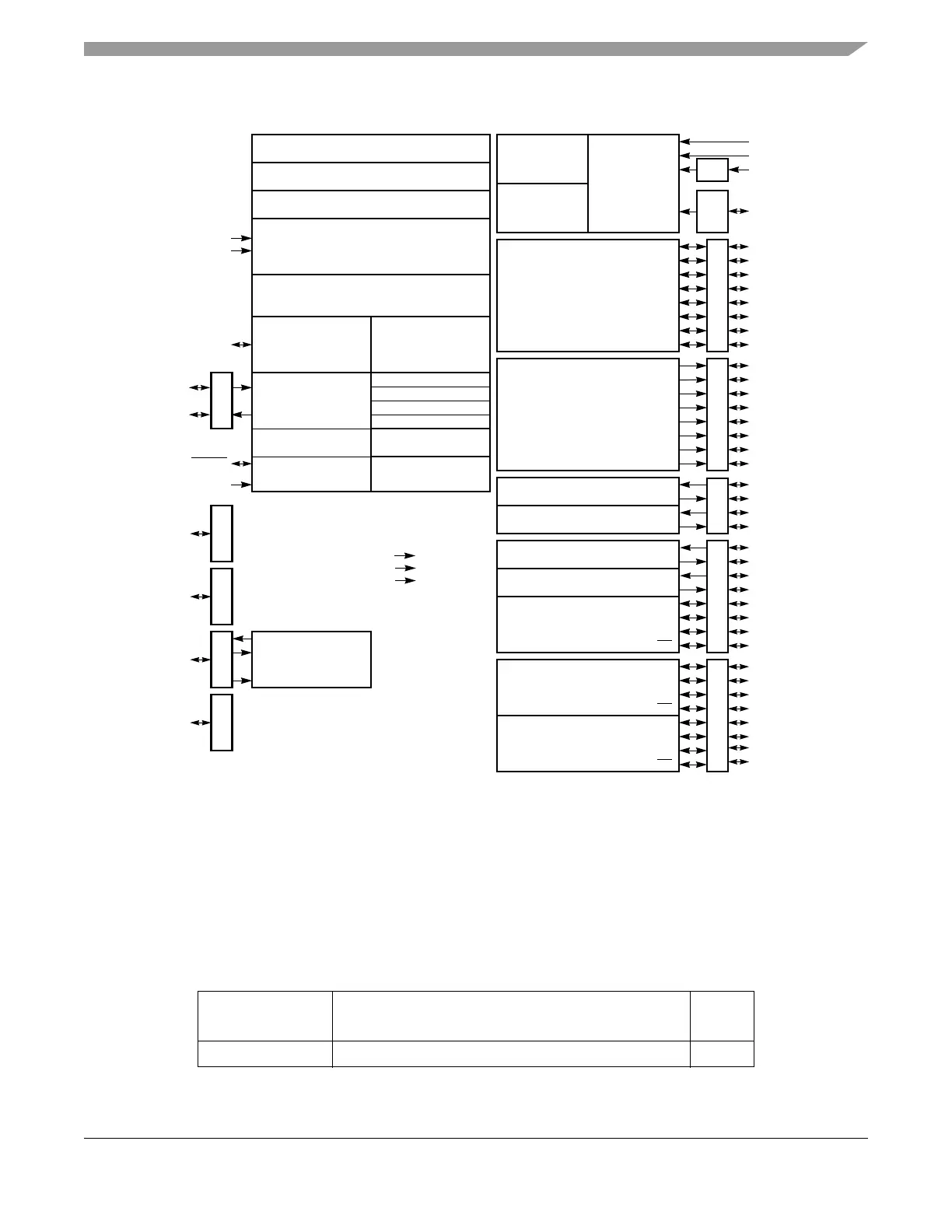

Figure 1-1. MC9S12G-Family Block Diagram

1.6 Family Memory Map

Table 1-3 shows the MC9S12G-Family register memory map.

Table 1-3. Device Register Memory Map

Address Module

Size

(Bytes)

0x0000–0x0009 PIM (Port Integration Module

) 10

1K … 11K bytes RAM

RESET

EXTAL

XTAL

0.5K … 4K bytes EEPROM with ECC

BKGD

VDDR

Real Time Interrupt

Clock Monitor

Single-wire Background

TEST

Debug Module

ADC

Interrupt Module

(WU Int)

SCI0

PS3

PS0

PS1

PS2

PTS

AN[15:0]

PAD[15:0]

8...16 ch.

16-bit 6 … 8 channel

Timer

TIM

Asynchronous Serial IF

8-bit 6 … 8 channel

Pulse Width Modulator

PWM

PB[7:0]

PTB

PA[7:0]

PTA

16K … 240K bytes Flash with ECC

CPU12-V1

COP Watchdog

PLL with Frequency

Modulation option

Debug Module

3 comparators

64 Byte Trace Buffer

Reset Generation

and Test Entry

RXD

TXD

PJ2

PTJ (Wake-up Int)

CAN

PM3

PM0

PM1

PM2

PTM

msCAN 2.0B

RXCAN

TXCAN

Auton. Periodic Int.

PJ7

PJ6

PT3

PT0

PT1

PT2

PTT

PT7

PT4

PT5

PT6

PP3

PP0

PP1

PP2

PTP (Wake-up Int)

PP7

PP4

PP5

PWM3

PWM0

PWM1

PWM2

PWM4

PWM5

IOC3

IOC0

IOC1

IOC2

IOC7

IOC4

IOC5

IOC6

VDDA

VSSA

VRH

VDDX1/VSSX1

VDDX2/VSSX2

PJ0

PJ1

3-5V IO Supply

VSS

Low Power Pierce

Oscillator

PP6

PWM6

PWM7

SCI1

Asynchronous Serial IF

RXD

TXD

MOSI

S

S

SCK

MISO

SPI0

Synchronous Serial IF

PS4

PS5

PS6

PS7

SCI2

Asynchronous Serial IF

RXD

TXD

Voltage Regulator

Input: 3.13V – 5.5V

Block Diagram shows the maximum configuration!

MOSI

S

S

SCK

MISO

SPI1

Synchronous Serial IF

MOSI

S

S

SCK

MISO

SPI2

Synchronous Serial IF

PJ3

PJ4

PJ5

PD[7:0]

PTD

PC[7:0]

PTC

VDDX3/VSSX3

Not all pins or all peripherals are available on all devices and packages.

Rerouting options are not shown.

PE0

PTE

PE1

PTAD

Analog-Digital

Converter

ACMP

Analog

Comparator

DAC0

Digital-Analog

Converter

AMPM

AMP

DACU

AMPP

DAC1

Digital-Analog

Converter

12-bit or 10-bit

RVA

Internal RC Oscillator

Loading...

Loading...