Port Integration Module (S12GPIMV1)

MC9S12G Family Reference Manual Rev.1.27

244 NXP Semiconductors

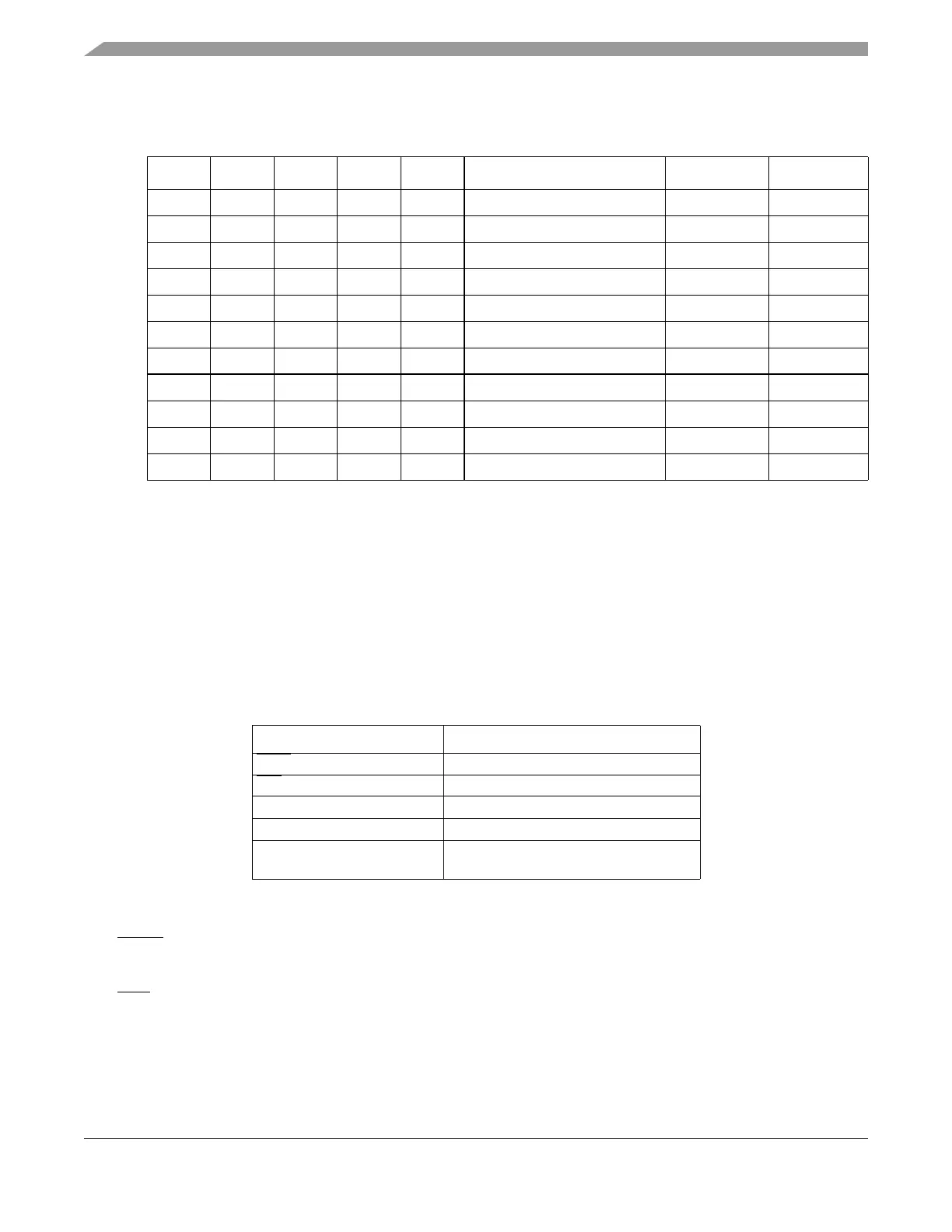

Table 2-92. Pin Configuration Summary

2.5.4 Interrupts

This section describes the interrupts generated by the PIM and their individual sources. Vector addresses

and interrupt priorities are defined at MCU level.

2.5.4.1 XIRQ, IRQ Interrupts

The XIRQ pin allows requesting non-maskable interrupts after reset initialization. During reset, the X bit

in the condition code register is set and any interrupts are masked until software enables them.

The IRQ

pin allows requesting asynchronous interrupts. The interrupt input is disabled out of reset. To

enable the interrupt the IRQCR[IRQEN] bit must be set and the I bit cleared in the condition code register.

The interrupt can be configured for level-sensitive or falling-edge-sensitive triggering. If IRQCR[IRQEN]

is cleared while an interrupt is pending, the request will deassert.

DDR IO PE PS

1

1

Always “0” on port A, B, C, D, BKGD. Always “1” on port E

IE

2

2

Applicable only on port P, J and AD.

Function Pull Device Interrupt

0 x 0 x 0 Input

3

3

Port AD: Assuming digital input buffer enabled in ADC module (ATDDIEN) and ACMP module (ACDIEN)

Disabled Disabled

0x100Input

3

Pullup Disabled

0x110Input

3

Pulldown Disabled

0x001Input

3

Disabled Falling edge

0x011Input

3

Disabled Rising edge

0x101Input

3

Pullup Falling edge

0x111Input

3

Pulldown Rising edge

1 0 x x 0 Output, drive to 0 Disabled Disabled

1 1 x x 0 Output, drive to 1 Disabled Disabled

1 0 x 0 1 Output, drive to 0 Disabled Falling edge

1 1 x 1 1 Output, drive to 1 Disabled Rising edge

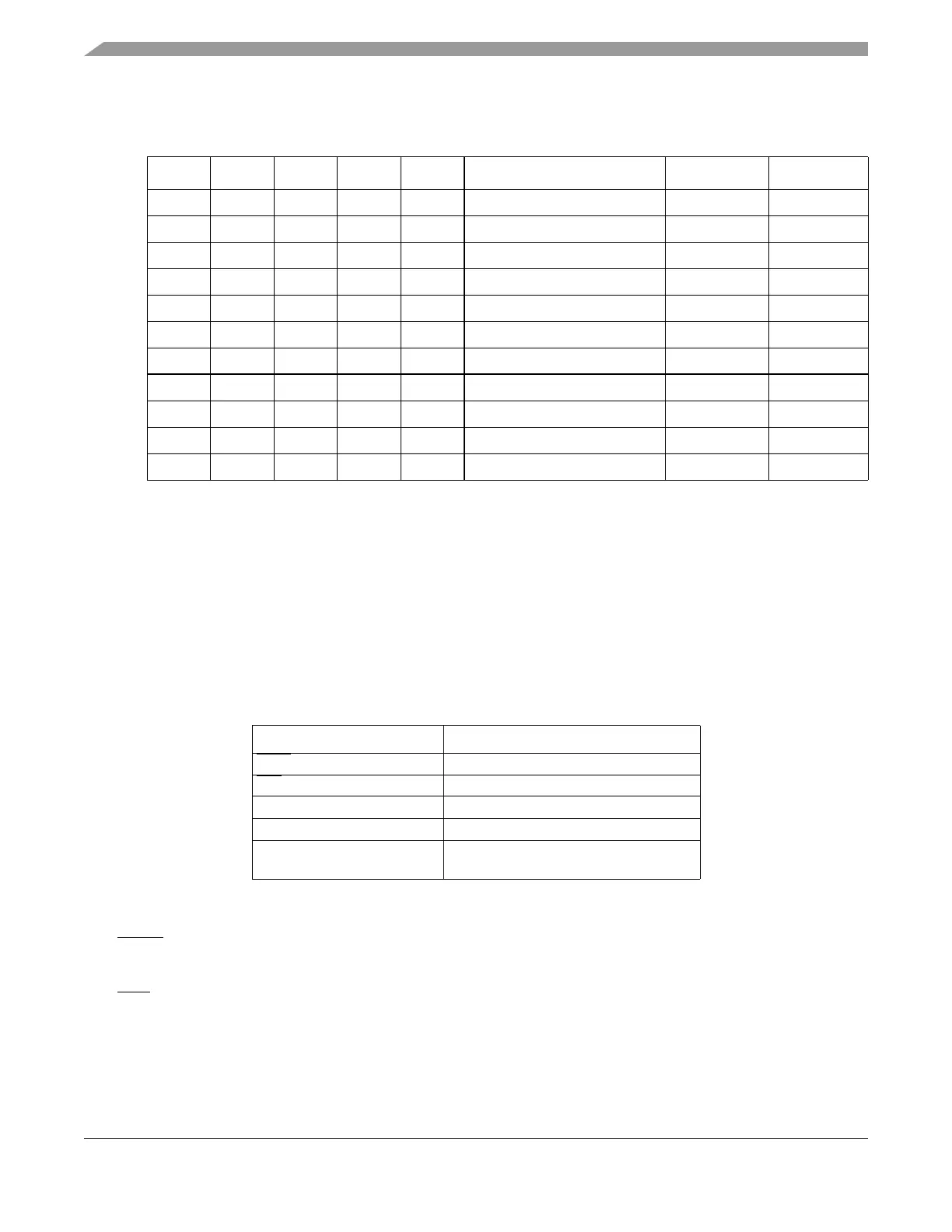

Table 2-93. PIM Interrupt Sources

Module Interrupt Sources Local Enable

XIRQ None

IRQ

IRQCR[IRQEN]

Port P pin interrupt PIEP[PIEP7-PIEP0]

Port J pin interrupt PIEJ[PIEJ7-PIEJ0]

Port AD pin interrupt PIE0AD[PIE0AD7-PIE0AD0]

PIE1AD[PIE1AD7-PIE1AD0]

Loading...

Loading...