MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 865

Chapter 26

48 KByte Flash Module (S12FTMRG48K1V1)

26.1 Introduction

The FTMRG48K1 module implements the following:

• 48Kbytes of P-Flash (Program Flash) memory

• 1,536bytes of EEPROM memory

The Flash memory is ideal for single-supply applications allowing for field reprogramming without

requiring external high voltage sources for program or erase operations. The Flash module includes a

memory controller that executes commands to modify Flash memory contents. The user interface to the

memory controller consists of the indexed Flash Common Command Object (FCCOB) register which is

written to with the command, global address, data, and any required command parameters. The memory

controller must complete the execution of a command before the FCCOB register can be written to with a

new command.

CAUTION

A Flash word or phrase must be in the erased state before being

programmed. Cumulative programming of bits within a Flash word or

phrase is not allowed.

The Flash memory may be read as bytes and aligned words. Read access time is one bus cycle for bytes

and aligned words. For misaligned words access, the CPU has to perform twice the byte read access

command. For Flash memory, an erased bit reads 1 and a programmed bit reads 0.

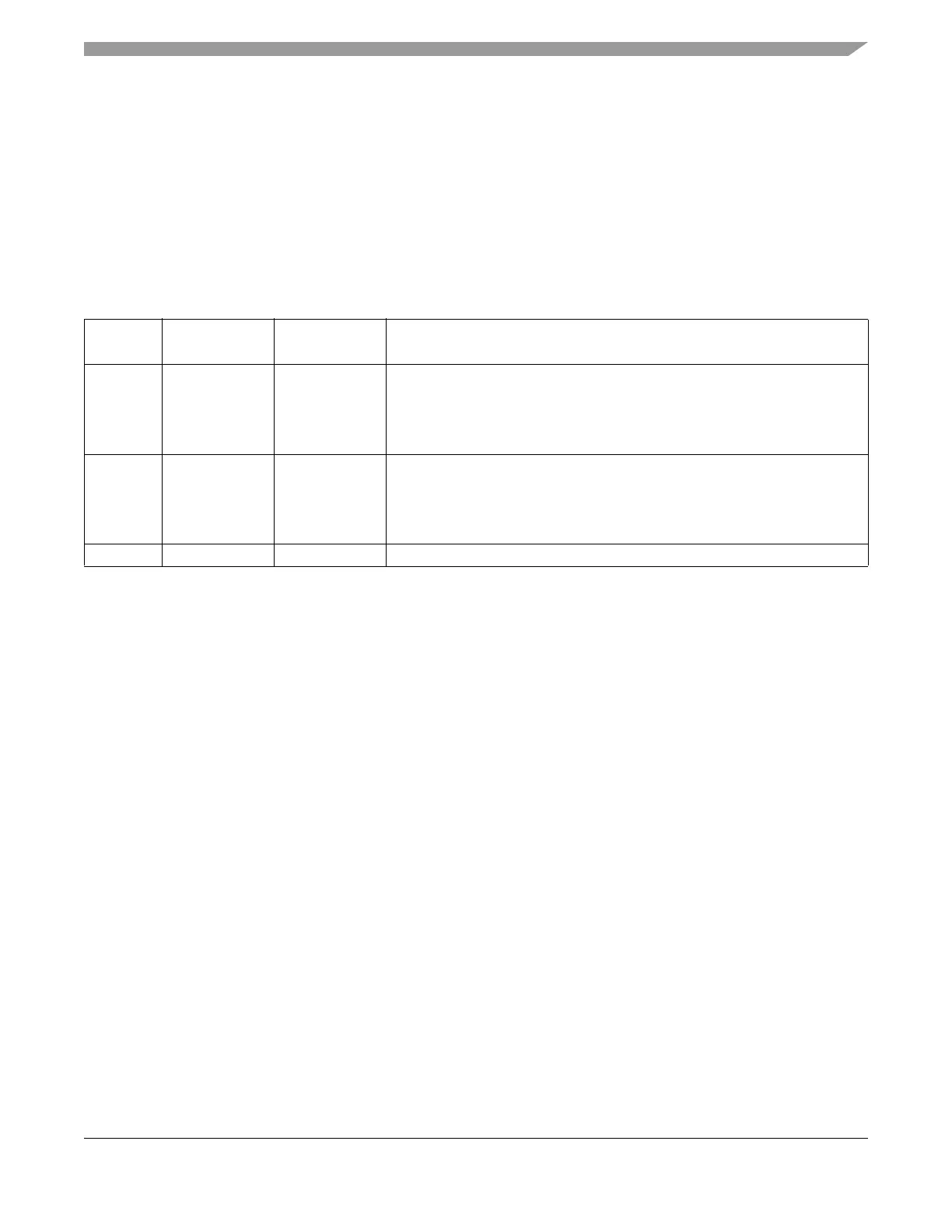

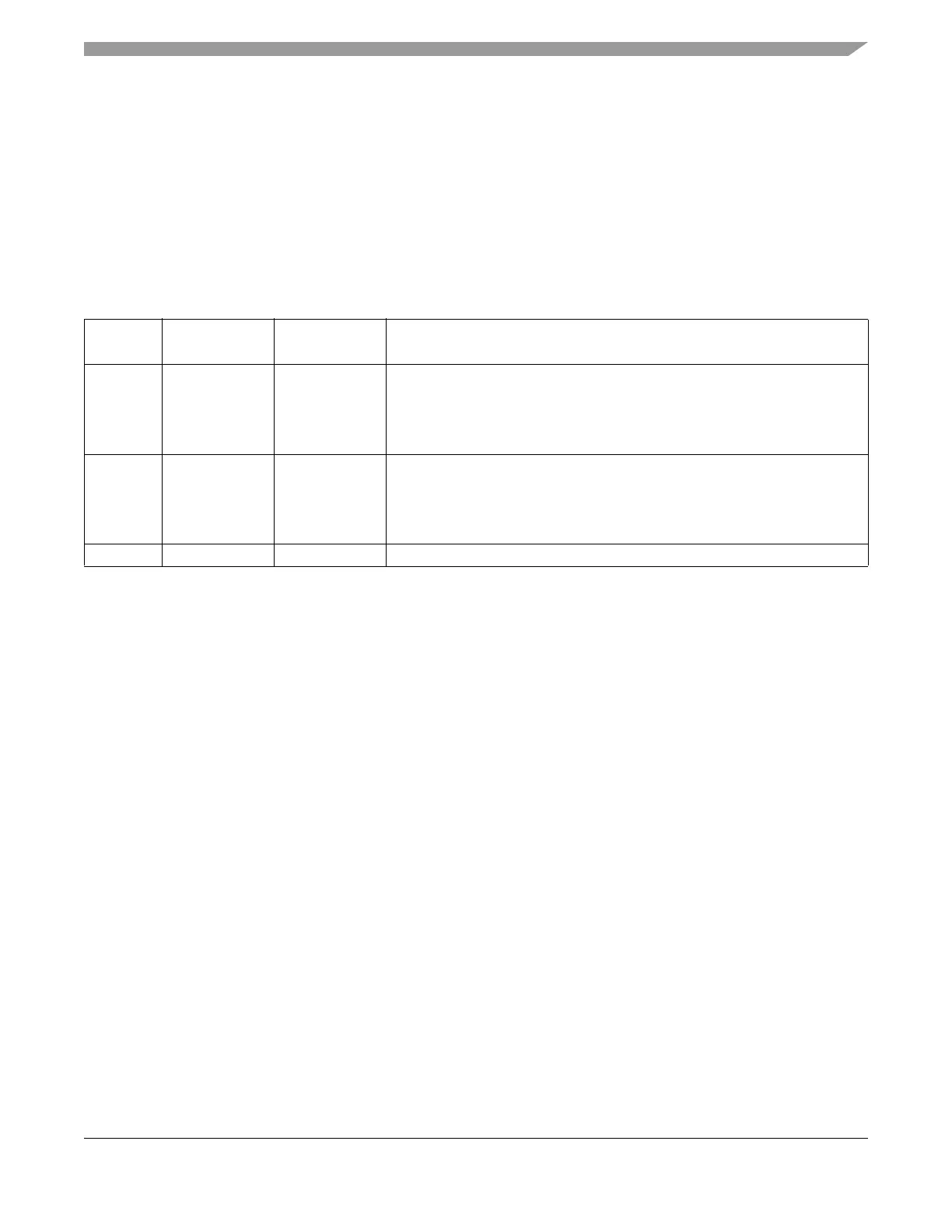

Table 26-1. Revision History

Revision

Number

Revision

Date

Sections

Affected

Description of Changes

V01.04 17 Jun 2010 26.4.6.1/26-899

26.4.6.2/26-900

26.4.6.3/26-900

26.4.6.14/26-91

0

Clarify Erase Verify Commands Descriptions related to the bits MGSTAT[1:0]

of the register FSTAT.

V01.05 20 aug 2010 26.4.6.2/26-900

26.4.6.12/26-90

7

26.4.6.13/26-90

9

Updated description of the commands RD1BLK, MLOADU and MLOADF

Rev.1.27 31 Jan 2011 26.3.2.9/26-882 Updated description of protection on Section 26.3.2.9

Loading...

Loading...