Scalable Controller Area Network (S12MSCANV3)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 619

18.4.5.7 Disabled Mode

The MSCAN is in disabled mode out of reset (CANE=0). All module clocks are stopped for power saving,

however the register map can still be accessed as specified.

18.4.5.8 Programmable Wake-Up Function

The MSCAN can be programmed to wake up from sleep or power down mode as soon as CAN bus activity

is detected (see control bit WUPE in MSCAN Control Register 0 (CANCTL0). The sensitivity to existing

CAN bus action can be modified by applying a low-pass filter function to the RXCAN input line (see

control bit WUPM in Section 18.3.2.2, “MSCAN Control Register 1 (CANCTL1)”).

This feature can be used to protect the MSCAN from wake-up due to short glitches on the CAN bus lines.

Such glitches can result from—for example—electromagnetic interference within noisy environments.

18.4.6 Reset Initialization

The reset state of each individual bit is listed in Section 18.3.2, “Register Descriptions,” which details all

the registers and their bit-fields.

18.4.7 Interrupts

This section describes all interrupts originated by the MSCAN. It documents the enable bits and generated

flags. Each interrupt is listed and described separately.

18.4.7.1 Description of Interrupt Operation

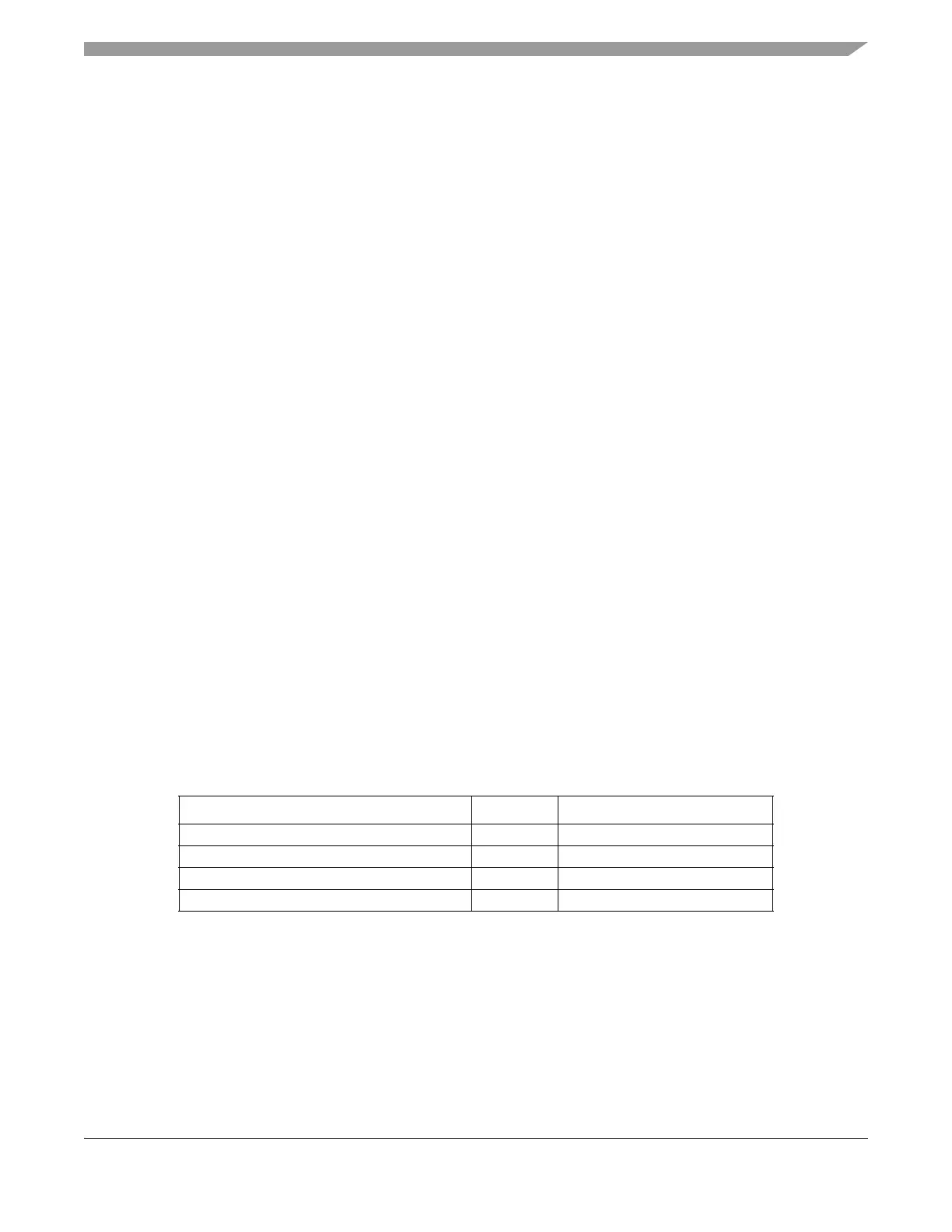

The MSCAN supports four interrupt vectors (see Table 18-39), any of which can be individually masked

(for details see Section 18.3.2.6, “MSCAN Receiver Interrupt Enable Register (CANRIER)” to

Section 18.3.2.8, “MSCAN Transmitter Interrupt Enable Register (CANTIER)”).

Refer to the device overview section to determine the dedicated interrupt vector addresses.

18.4.7.2 Transmit Interrupt

At least one of the three transmit buffers is empty (not scheduled) and can be loaded to schedule a message

for transmission. The TXEx flag of the empty message buffer is set.

Table 18-39. Interrupt Vectors

Interrupt Source CCR Mask Local Enable

Wake-Up Interrupt (WUPIF) I bit CANRIER (WUPIE)

Error Interrupts Interrupt (CSCIF, OVRIF) I bit CANRIER (CSCIE, OVRIE)

Receive Interrupt (RXF) I bit CANRIER (RXFIE)

Transmit Interrupts (TXE[2:0]) I bit CANTIER (TXEIE[2:0])

Loading...

Loading...