MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 533

Chapter 16

Analog-to-Digital Converter (ADC12B16CV2)

Revision History

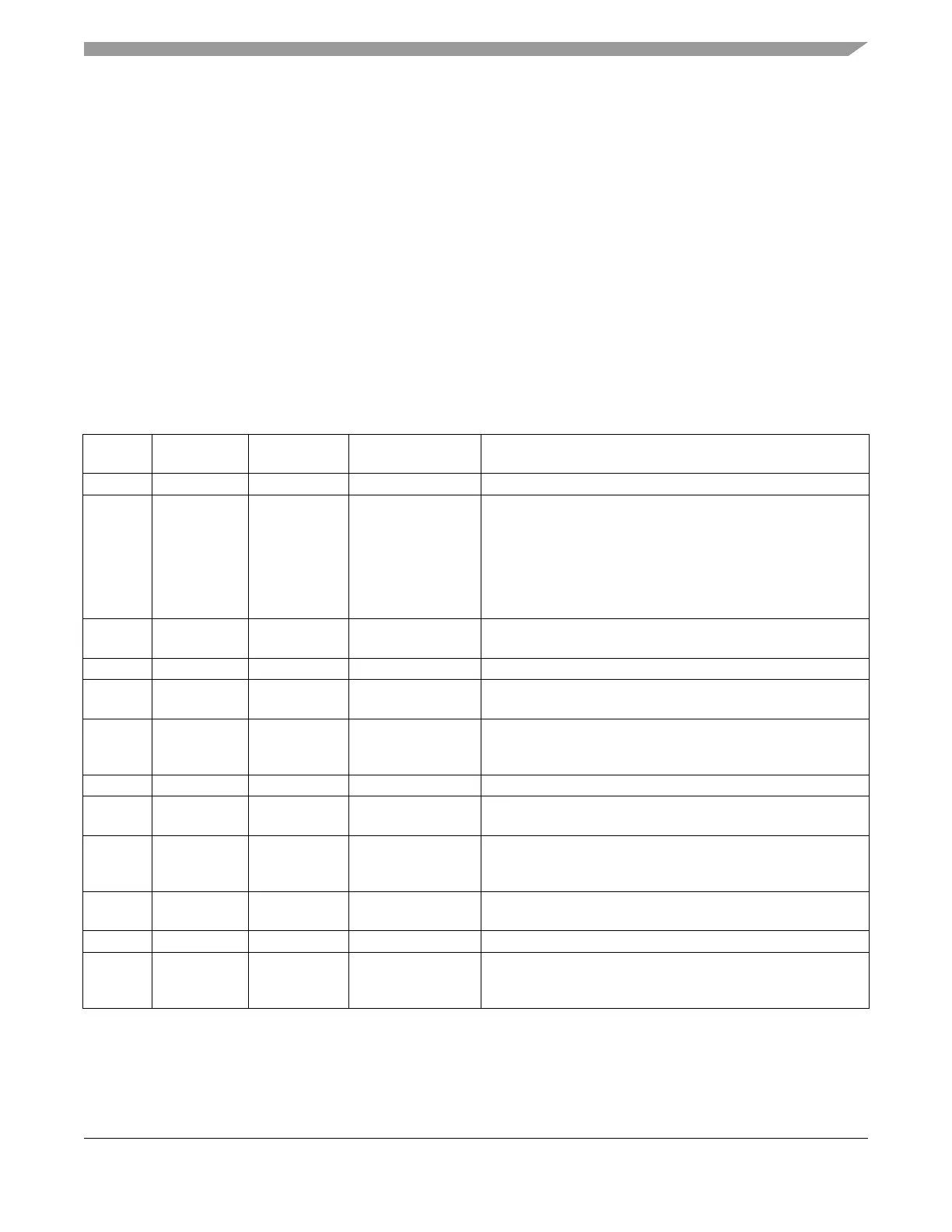

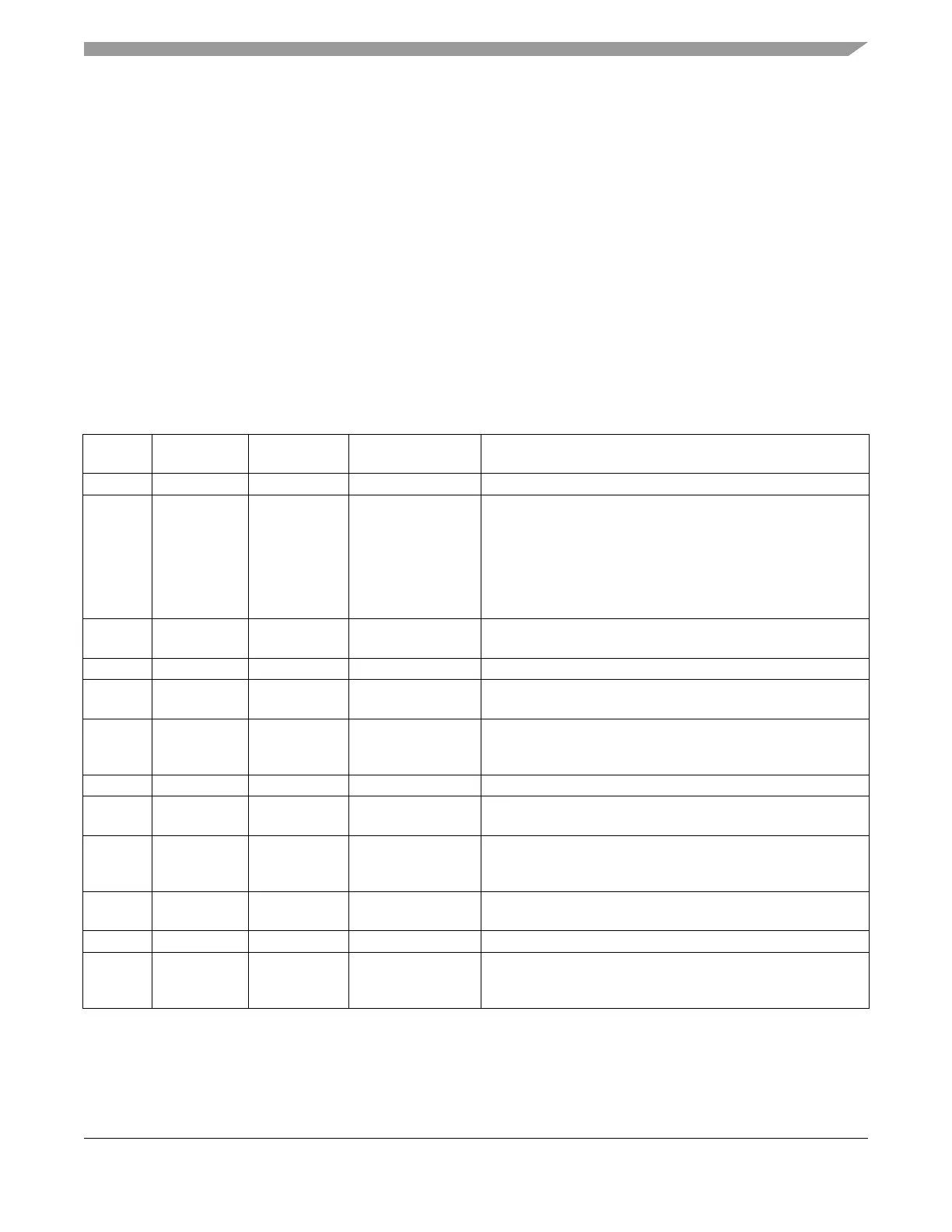

Version

Number

Revision

Date

Effective

Date

Author Description of Changes

V02.00 18 June 2009 18 June 2009 Initial version copied 12 channel block guide

V02.01 09 Feb 2010 09 Feb 2010

Updated Table 16-15 Analog Input Channel Select Coding -

description of internal channels.

Updated register ATDDR (left/right justified result) description

in section 16.3.2.12.1/16-554 and 16.3.2.12.2/16-555 and

added Table 16-21 to improve feature description.

Fixed typo in Table 16-9 - conversion result for 3mV and 10bit

resolution

V02.03 26 Feb 2010 26 Feb 2010

Corrected Table 16-15 Analog Input Channel Select Coding -

description of internal channels.

V02.04 26 Mar 2010 16 Mar 2010 Corrected typo: Reset value of ATDDIEN register

V02.05 14 Apr 2010 14 Apr 2010

Corrected typos to be in-line with SoC level pin naming

conventions for VDDA, VSSA, VRL and VRH.

V02.06 25 Aug 2010 25 Aug 2010

Removed feature of conversion during STOP and general

wording clean up done in Section 16.4, “Functional

Description

v02.07 09 Sep 2010 09 Sep 2010 Update of internal only information.

V02.08 11 Feb 2011 11 Feb 2011

Connectivity Information regarding internal channel_6 added

to Table 16-15.

V02.09 29 Mar 2011 29 Mar 2011

Fixed typo in bit description field Table 16-14 for bits CD, CC,

CB, CA. Last sentence contained a wrong highest channel

number (it is not AN7 to AN0 instead it is AN15 to AN0).

V02.10 22. Jun 2012 22. Jun 2012

Updated register wirte access information in section

16.3.2.9/16-552

V02.11 29. Jun 2012 29. Jun 2012 Removed IP name in block diagram Figure 16-1

V02.12 02 Oct 2012 02 Oct 2012

Added user information to avoid maybe false external trigger

events when enabling the external trigger mode

(Section 16.4.2.1, “External Trigger Input).

Loading...

Loading...