Electrical Characteristics

MC9S12G Family Reference Manual Rev.1.27

1216 NXP Semiconductors

A.7.2 NVM Reliability Parameters

The reliability of the NVM blocks is guaranteed by stress test during qualification, constant process

monitors and burn-in to screen early life failures.

The data retention and program/erase cycling failure rates are specified at the operating conditions noted.

The program/erase cycle count on the sector is incremented every time a sector or mass erase event is

executed.

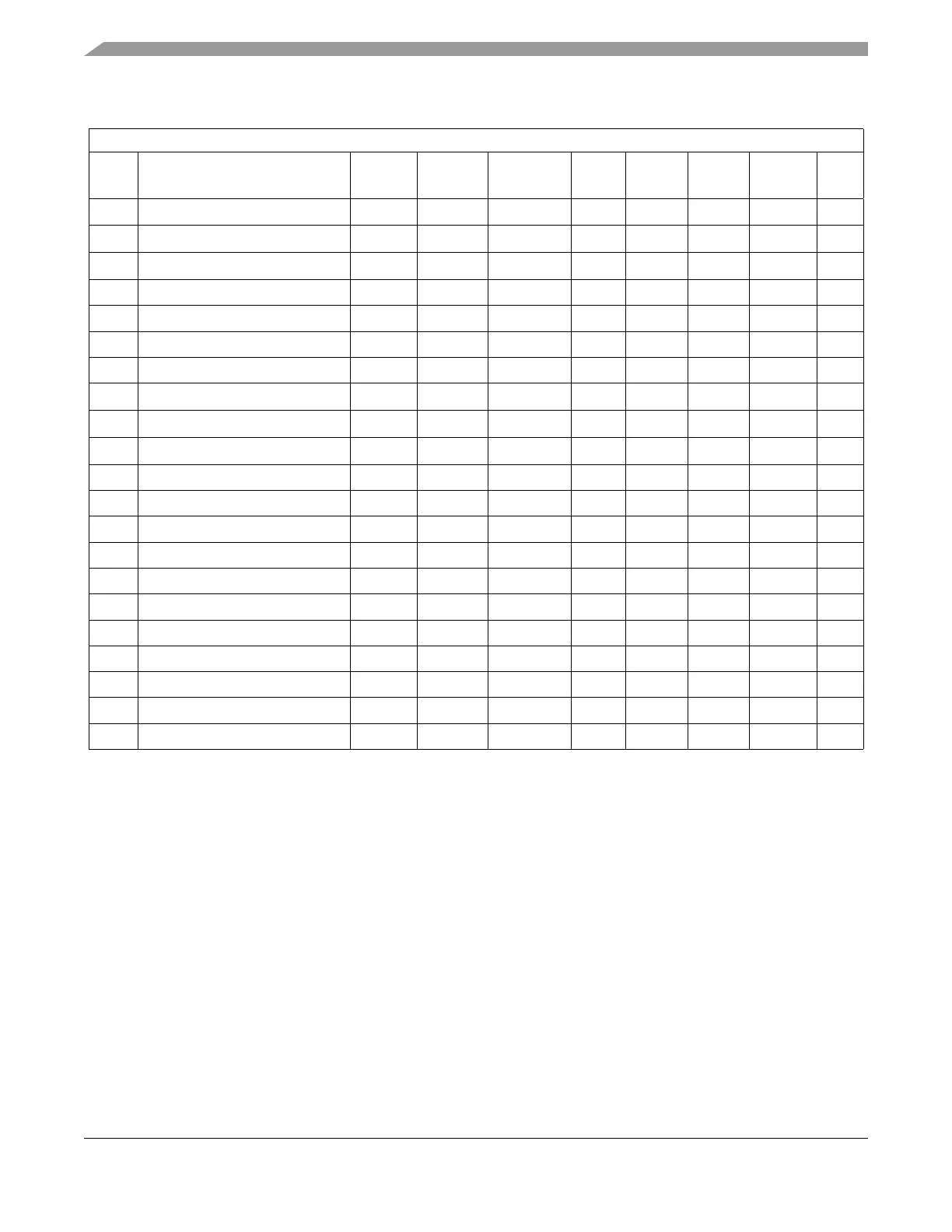

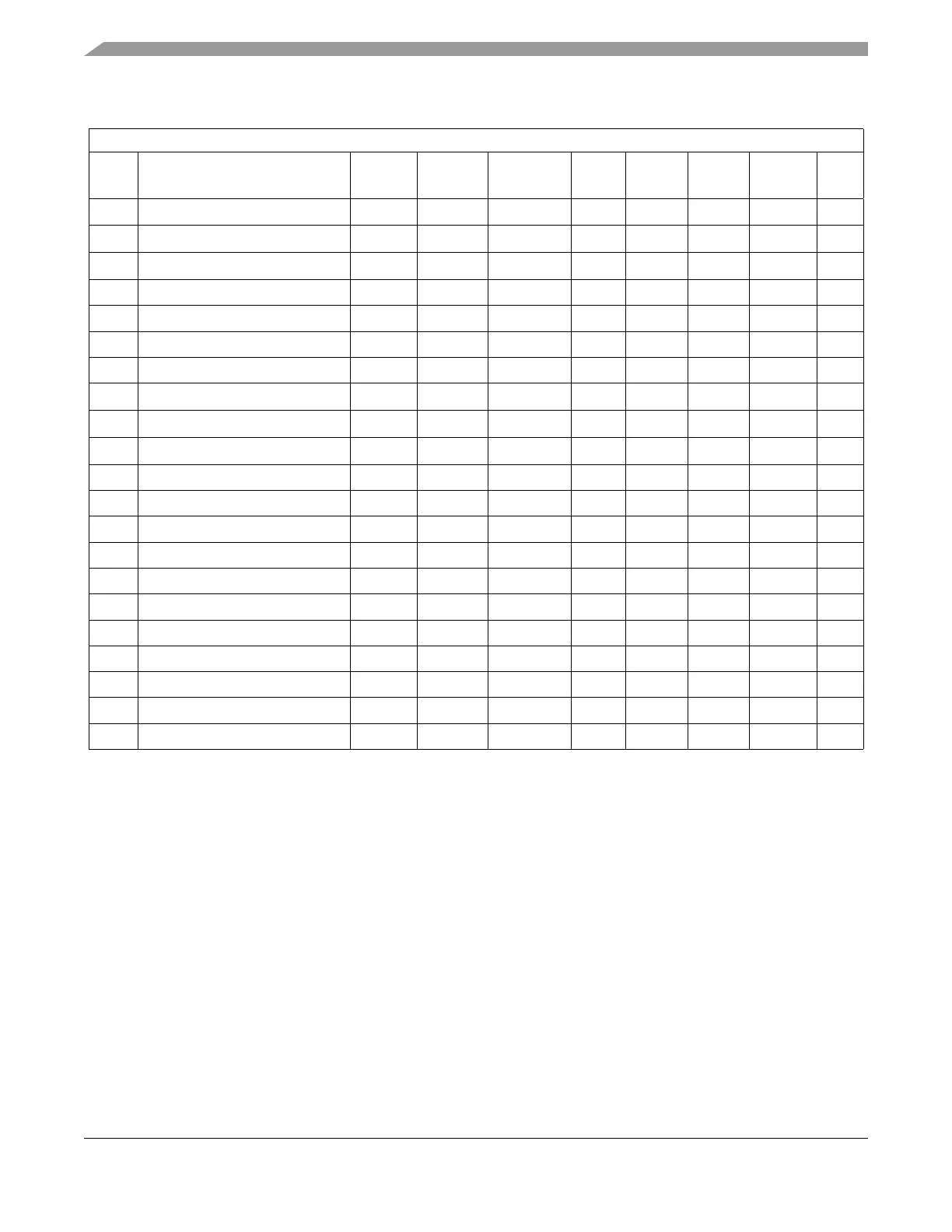

Table A-38. NVM Timing Characteristics)

S12G192, S12GA192, S12G240, S12GA240

Num Command

f

NVMOP

cycle

f

NVMBUS

cycle

Symbol Min

1

Typ

2

Max

3

Lfmax

4

Unit

1

Erase Verify All Blocks

5,6

0 64361

t

RD1ALL

2.57 2.57 5.15 128.72 ms

2

Erase Verify Block (Pflash)

5

0 62128

t

RD1BLK_P

2.49 2.49 4.97 124.26 ms

3

Erase Verify Block (EEPROM)

6

02586

t

RD1BLK_D

0.1 0.1 0.21 5.17 ms

4 Erase Verify P-Flash Section 0 606

t

RD1SEC

0.02 02 0.05 1.21 ms

5 Read Once 0 516

t

RDONCE

20.64 20.64 20.64 516 s

6 Program P-Flash (4 Word) 164 3014

t

PGM_4

0.28 0.28 0.65 12.26 ms

7 Program Once 164 2960

t

PGMONCE

0.27 0.28 0.28 3.17 ms

8

Erase All Blocks

5,6

200126 65067

t

ERSALL

193.2 202.73 205.33 380.29 ms

9

Erase Flash Block (Pflash)

5

200120 62651

t

ERSBLK_P

193.1 202.63 205.13 375.45 ms

10

Erase Flash Block (EEPROM)

6

100060 2871

t

ERSBLK_D

95.41 100.17 100.29 130.82 ms

11 Erase P-Flash Sector 20015 962

t

ERSPG

19.1 20.05 20.09 26.94 ms

12 Unsecure Flash 200126 65145

t

UNSECU

193.2 202.73 205.34 380.45 ms

13 Verify Backdoor Access Key 0 549

t

VFYKEY

21.96 21.96 21.96 549 s

14 Set User Margin Level 0 426

t

MLOADU

17.04 17.04 17.04 426 s

15 Set Factory Margin Level 0 435

t

MLOADF

17.4 17.4 17.4 435 s

16 Erase Verify EEPROM Section 0 582

t

DRD1SEC

0.02 0.02 0.05 1.16 ms

17 Program EEPROM (1 Word) 68 1585

t

DPGM_1

0.13 0.13 0.32 6.43 ms

18 Program EEPROM (2 Word) 136 2532

t

DPGM_2

0.23 0.24 0.54 10.3 ms

19 Program EEPROM (3 Word) 204 3479

t

DPGM_3

0.33 0.34 0.76 14.17 ms

20 Program EEPROM (4 Word) 272 4426

t

DPGM_4

0.44 0.45 0.98 18.04 ms

21 Erase EEPROM Sector 5015 777

t

DERSPG

4.81 5.05 20.59 38.28 ms

1

Minimum times are based on maximum f

NVMOP

and maximum f

NVMBUS

2

Typical times are based on typical f

NVMOP

and typical f

NVMBUS

3

Maximum times are based on typical f

NVMOP

and typical f

NVMBUS

plus aging

4

Lowest-frequency max times are based on minimum f

NVMOP

and minimum f

NVMBUS

plus aging

5

Affected by Pflash size

6

Affected by EEPROM size

Loading...

Loading...