S12S Debug Module (S12SDBGV2)

MC9S12G Family Reference Manual Rev.1.27

NXP Semiconductors 343

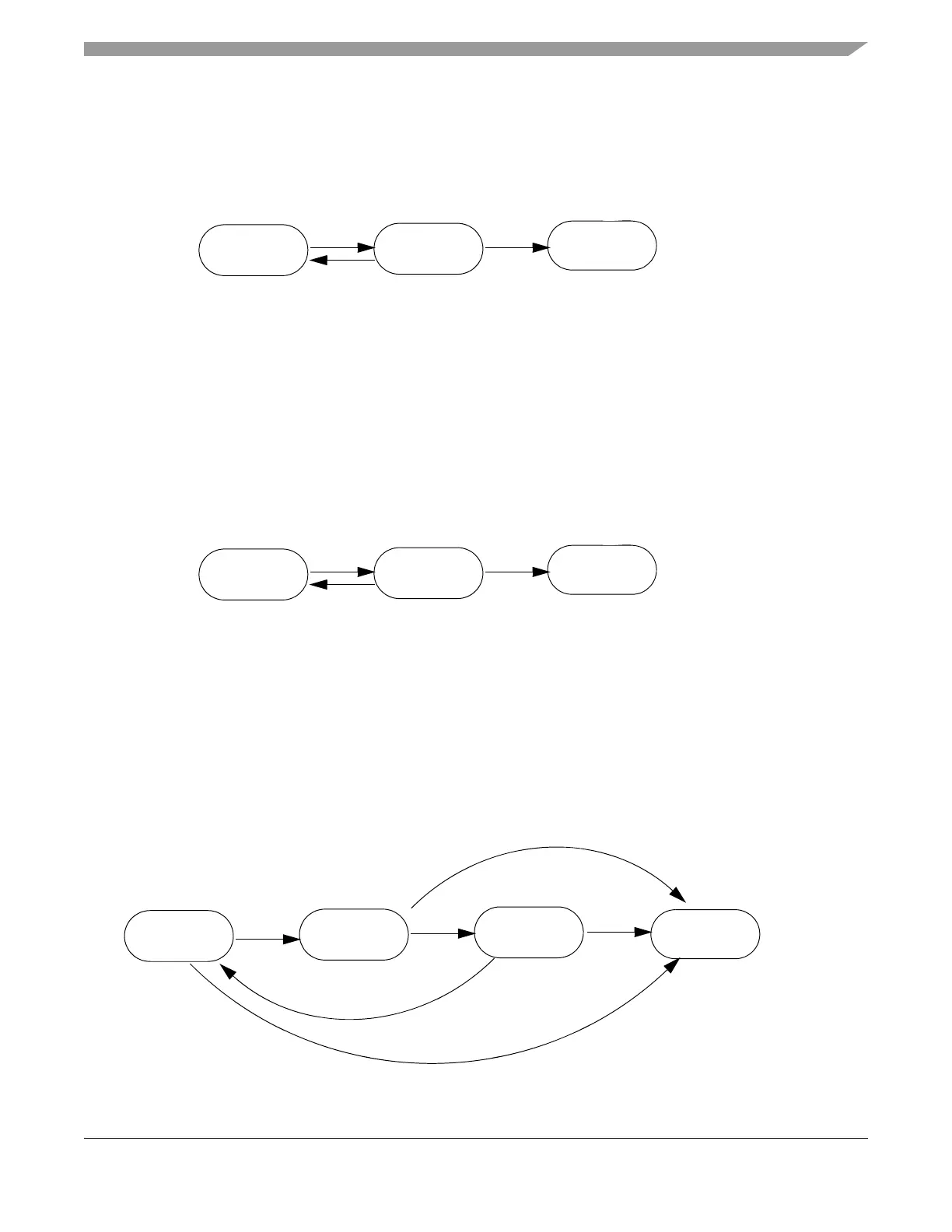

8.5.6 Scenario 5

Trigger if following event A, event C precedes event B. i.e. the expected execution flow is A->B->C.

Figure 8-34. Scenario 5

Scenario 5 is possible with the S12SDBGV1 SCR encoding

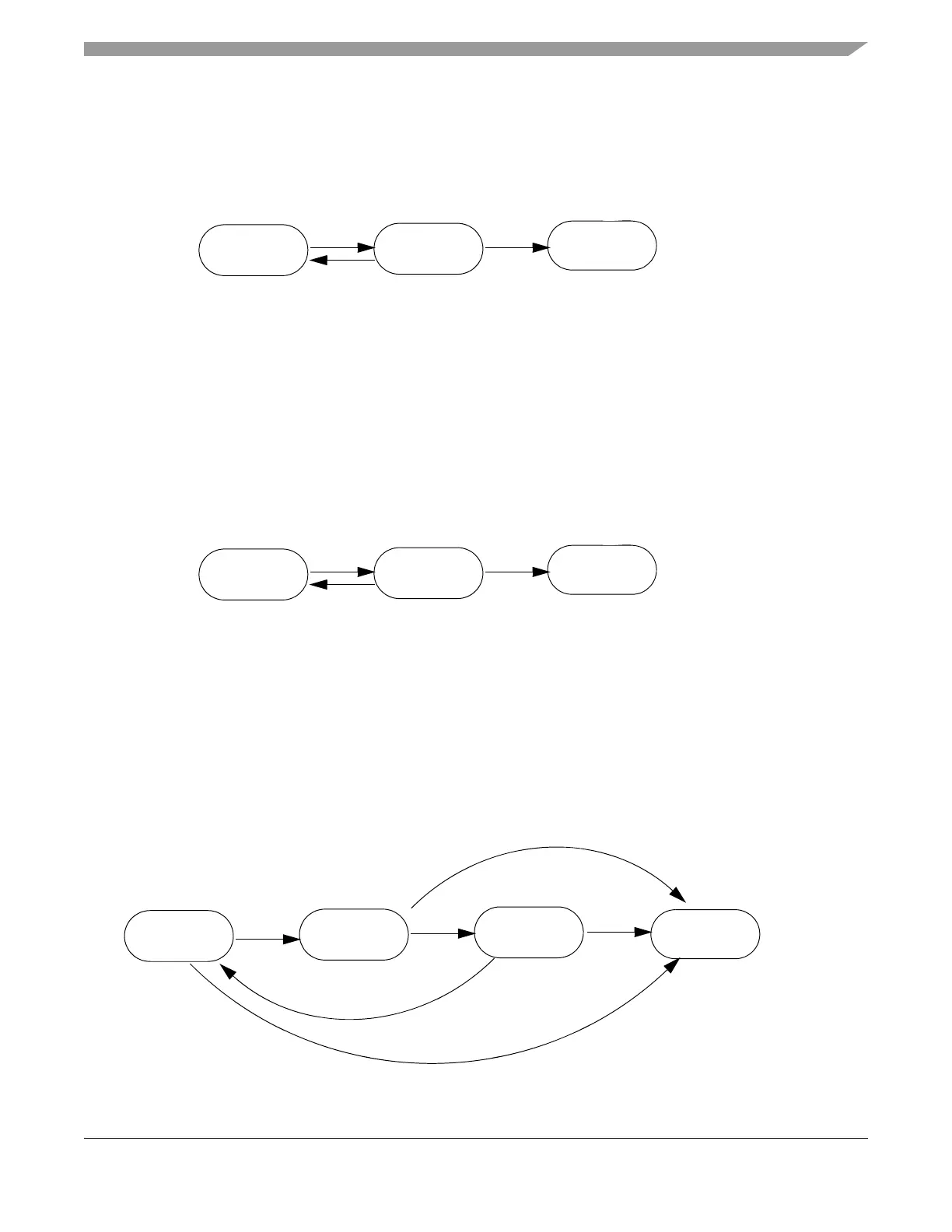

8.5.7 Scenario 6

Trigger if event A occurs twice in succession before any of 2 other events (BC) occurs. This scenario is

not possible using the S12SDBGV1 SCR encoding. S12SDBGV2 includes additions shown in red. The

change in SCR1 encoding also has the advantage that a State1->State3 transition using M0 is now possible.

This is advantageous because range and data bus comparisons use channel0 only.

Figure 8-35. Scenario 6

8.5.8 Scenario 7

Trigger when a series of 3 events is executed out of order. Specifying the event order as M1,M2,M0 to run

in loops (120120120). Any deviation from that order should trigger. This scenario is not possible using the

S12SDBGV1 SCR encoding because OR possibilities are very limited in the channel encoding. By adding

OR forks as shown in red this scenario is possible.

Figure 8-36. Scenario 7

State1

Final State

State2

SCR1=0011

SCR2=0110

M1

M0

M2

State1

Final State

State3

SCR1=1001

SCR3=1010

M0

M0

M12

State1

Final State

State3

State2

SCR1=1101

SCR2=1100

SCR3=1101

M1

M2

M12

M0

M02

M01

Loading...

Loading...